超声相控阵系统中高精度相控发射与接收的实现

摘 要:本文描述了如何利用FPGA在系统中实现高精度相控发射与接收。所有的发射和接收参数PC机计算并通过ISA总线写入FPGA的。

关键词:相控阵;超声检测;电子扫查;FPGA

引言

超声检测在各种工程上有着非常广泛的应用,而且声束聚焦对于超声诊断也愈来愈重要,因为人们总是希望看到更小、更细微的组织结构,这不仅要求提高工作频率、而且要求声束聚焦。声束的聚焦类似于光束通过透镜的原理,最简单的方法是将换能器直接作成凹面阵实现聚焦。但此时其焦点是固定的,而在超声聚焦应用中都常需要调整焦点(改变焦距和聚焦的方向),如用机械方法调焦很不方便,速度也慢。超声相控阵的方法是用电子技术调整焦点位置和聚焦的方向,它的基本思想是控制超声探头中不同单元之间的触发延时时序,在精确的延时时序控制下,不同单元发出的超声波在空间发生干涉,产生所需要的合成波束(见图1)。相控超声波的这种特性非常适合于无损检测。首先可以通过电子切换选用不同的单元,实现波束的快速移动(即电子扫查),明显提高缺陷的检测效率,比单个单元的常规探头检测速度快一个数量级。其次相控超声波束很容易实现波束偏转,不用移动探头就可以实现动态“扇扫”。当然这也要归功于现代集成电路技术发展,因为发射与接收的延时控制在纳秒级,而且信号的采样与处理需要很高的吞吐量,针对上述特点,采用FPGA技术研制一套数字式多通道信号发射与接收设备已成为可能。

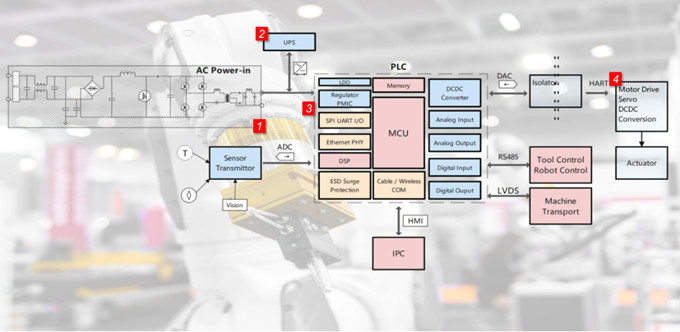

图1 相控超声波束偏转与聚焦控制延时时序示意图

FPGA在系统中的应用

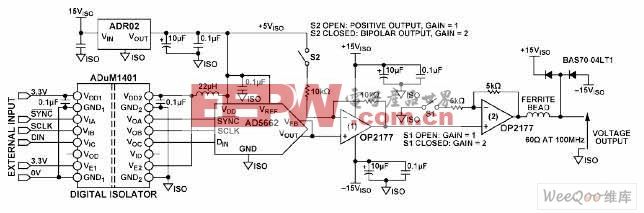

由于该系统涉及到许多控制信号的时序配合和大容量数据的缓冲问题,采用FPGA可以很好的满足系统要求。比如Altera的Cyclone系列的EP1C3具有的单元数、RAM以及I/O管脚等非常适合本文描述的系统。围绕FPGA的系统设计示意图见图2。该相控阵系统采用2个64单元的探头,通过四选一开关切换电路实现波束的快速移动。由于发射与接收的延时控制在纳秒级,即使FPGA的时钟为100MHz,延时控制精度也只能做到10ns。如果通过提高FPGA的时钟频率来实现更高的延时控制精度,将给电路设计带来困难,并且成本也加大,故采用精度为2ns的延时线实现10ns以内的延时要求,此时FPGA只需要3根I/O线用来控制选通延时线就可以实现10ns以内的延时要求。

图2 FPGA在发射与接收延时控制中的应用

利用FPGA内部的大容量RAM对接收的超声信号进行缓存与合成延时控制。这种延时控制可以通过图3进行解释。在FPGA中为每一路参与合成的超声波束开辟一个相同容量的buffer(比如2kbytes)。当信号到达时,buffer的写允许,采集一定数据量后,如果还有波束未到达就延时等待,直到参与合成的所有波束到达并采集后,所有buffer的读同时允许,通过D/A和模拟加法电路就可以实现超声波束的合成了。当然,利用FPGA的buffer实现的延时精度只有10ns,所以D/A后面仍然需要延时线配合。表1.列出了上位机需要写给FPGA的控制参数,这些参数通过ISA总线,以word(16bits)的形式写入,其中包括发射延时、发射选通允许、发射四选一开关、发射脉宽、Buffer的大小、接收选通允许、A/D转换开始时间、接收四选一开关以及接收延时等待。

图 3. 利用FPGA内部RAM对接收波束进行缓存与合成控制

表1 上位机需要写给FPGA的控制参数

发射延时控制:10ns级延时,13bits

2ns级延时,3bits

选通

发开关

空,保留

发射脉宽(10ns级),8bits

超声波Buffer的大小,16bits

选通

A/D转换开始时间(也就是Buffer写允许相对于同步脉冲延时),10ns级,15bits

收开关

接收延时等待,10ns级,11bits

2ns级延时,3bits

精确延时控制验证方法

利用FPGA与延时线的方法实现精度为2ns的延时控制,对于发射来说,调试与验证比较容易,只需要一个多通道500MHz的示波器就可以了。从FPGA发射一个方波同步脉冲和一个方波激励脉冲,一级一级的往后测试,直至相控阵探头。通过示波器可以观察从FPGA到探头整个电路的系统延时以及激励脉冲相对于同步脉冲的延时间隔,该间隔由FPGA内部参数决定,并且可以修改。

对于接收延时控制是否准确的验证稍微困难一些。因为接收的不是方波脉冲,而是7.5MHz(探头单元固有频率)的近似正弦超声信号。为了验证延时控制是否正确,需要在超声波接收电路之前加上一个不连续的,只有若干周期的7.5MHz的正弦信号,一般的信号发生器没有这种功能。利用系统上的FPGA配合100MHz D/A比较容易产生这种特殊信号。采用VerilogHDL设计的FPGA程序如下:

reg [3:0] da_cnt; //正弦表指针

reg [15:0] da_encnt; //D/A允许计数器

reg daen; // D/A允许

assign AD_DATA_OUT = AD_test; //D/A数据总线

always @ (posedge CLK) //D/A允许控制da_encnt

begin

if(SYN_PULSE)da_encnt <= 16'b0;

else da_encnt <= da_encnt + 1;

end

always @ (posedge CLK) //daen

begin

if(da_encnt > 65) daen <= 1'b0; //一共输出5个周期

else daen <= 1'b1;

end

always @ (posedge CLK) //正弦表指针da_cnt修改

begin

if( (SYN_PULSE)||(da_cnt >= 12) ) da_cnt <= 4'b0;

else

begin

if(daen) da_cnt <= da_cnt + 1;

else da_cnt <= 4'b0;

end

end

always @ (posedge CLK) //通过D/A输出正弦表

begin

case(da_cnt[3:0])

4'b0000: AD_test <= 128; //0

4'b0001: AD_test <= 187;

4'b0010: AD_test <= 233;

4'b0011: AD_test <= 255;

4'b0100: AD_test <= 248;

4'b0101: AD_test <= 213;

4'b0110: AD_test <= 159;

4'b0111: AD_test <= 97;

4'b1000: AD_test <= 43;

4'b1001: AD_test <= 8;

4'b1010: AD_test <= 1;

4'b1011: AD_test <= 23;

4'b1100: AD_test <= 69; //12

default: AD_test <= 128; //13

endcase

end

通过上述方法可以产生出比较好的接近7.5MHz的若干周期的正弦波形,将该波形加到其它电路板超声波接收电路之前,可以验证接收延时控制是否准确。实验证明,FPGA加上延时线完全可以实现精度为2ns的超声波发射与接收延时控制的要求。

参考文献:

1. Michael Moles and Fabrice Cancre, "ELEMENT PARAMETERS FOR ULTRASONIC PHASED ARRAYS", CP615, Review of Quantitative Nondestructive Evaluation VoL 21, ed. by D. O. Thompson and D. E. Chimenti, pp855-860.

2. 钟志名, 梅德松, "超声相控阵技术的发展及应用", NDT, Vol.24, No.2, Feb. 2002,pp69-71.

评论