一种多体制通信时间同步算法及其FPGA实现

—— Timing Synchronization Algorithm for Multimode Communication and Implementation in FPGA

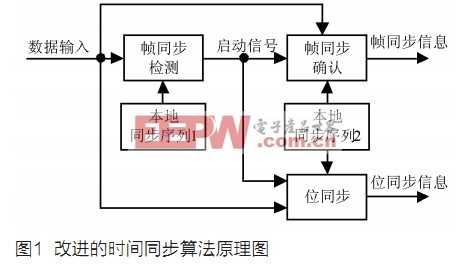

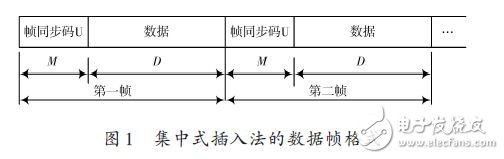

为了解决传统时间同步算法不适用于多种无线通信体制且不适于硬件实现等问题,本文提出了一种改进的时间同步算法,如图1所示。在改进的时间同步算法中,本地同步序列分成和两段,从而使帧同步和位同步都可以利用接收序列与本地同步序列的相关性实现。因此,只需要改变本地同步序列,改进后的时间同步算法就可以适用于不同的通信体制。

本文引用地址://m.amcfsurvey.com/article/116957.htm

在本地同步序列及其划分方式确定后,时间同步算法的工作原理如下:首先,系统利用本地同步序列1完成帧同步的初始检测。当检测结果认为接收到数据帧时,启动帧同步确认和位同步等模块,利用本地同步序列2完成帧同步确认和位同步调整。其中,帧同步检测使用改进的分段相关法,可以有效提高帧检测算法对载波频偏的容忍度,降低帧同步的漏同步概率,并使算法便于硬件实现。帧同步确认和位同步在帧同步检测成功后启动,通过本地同步序列2与接收序列的相关结果来确认帧同步检测结果是否正确,从而减少假同步概率,并同时利用接收序列与本地同步序列2之间的相关性完成位同步处理,大大加快了位同步的收敛速度。

评论