数字低通:名称虽然不同 却仍是一种滤波器

D:看起来不错。难道你要我告诉你数字等效(digital equivalent)?比方说,我需要平滑数字信号,像你想要平滑VRef信号的方式来消除噪声。

本文引用地址://m.amcfsurvey.com/article/124375.htmT:当我过滤一个VRef信号时,我试图消除“失真(fuzz)”,高频内容恰恰代表了噪声,而不是信号。你用数字信号做什么,使方形的位(square bits)变圆?

D:不是。当我们“平滑”数字信号时,我们希望消除代表噪声的快速变化,就是你说的VRef“失真”。

T:因此,一个有噪声的数字信号只是一组跳来跳去的(jump around)数字流吗?

D:是的。我们要平滑这些跳跃。

T:好了,那么我再问问,我的简单的RC滤波器数字等效是什么呢?

D:嗯,首先我们要看看你的模拟RC中的一个小细节。

T:这很简单,它有一个RxC的时间常数,它以20dB/decade(6dB/octave)的速度在2pRC(以弧度表示)的极点频率以上下降。

D:是这样。但是,在这种情况下,它更容易配合脉冲响应。脉冲响应非常容易。它只是一个指数衰减。

T:所以,脉冲迅速对电容器充电,然后电压随着电阻两端电荷的消耗而衰减。

D:是的。当然,我们永远都不会有真正的脉冲,但它们是有用的“数学小说(mathematical fiction)”。问题的关键在于RC滤波器呈指数衰减:衰减率永远与剩余的电压成正比,因为这决定了电阻中的电流。

T:好吧……是否你要看看时域。

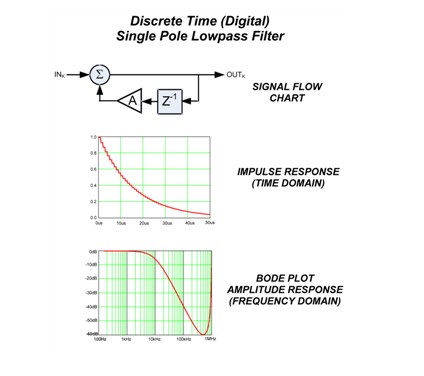

D:我们就在这一点。这里是数字等效:

图3:数字IIR LPF的脉冲响应和波特图

(图字:离散时间(数字)单极点低通滤波器;脉冲响应(时域);波特图振幅响应(频域))

T:等一下,我看到了一个加法器、一个增益模块,我假设z-1 是一个延迟块(delay block)。这些都是模拟块。我想我们是在讨论数字吧?

D:我们是在讨论数字。这些块的每一个都有模拟和数字表示。以加法器为例。

T:它可能只是一个电阻,或者是一个运算放大器电路。

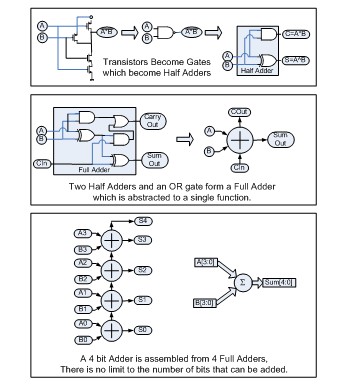

D:或者它也可以是一个数字门和一个加法器的集合。下面是我们如何构建一个数字加法器的方法:

图4:加法器——晶体管、门、半加器,加法器的演变

(图字:晶体管成为了多个门,门又成为了半加器。两个半加器和一个OR门来自于全加器,全加器抽象为一个函数。一个4位加法器是由4个全加器组装起来的。不会限制可以添加的位数。)

评论