采用低功耗28-nm FPGA降低系统总成本

例如,一个简单视频处理应用只需要9位精度,而一些高端彩色系统则需要24位。对于9位视频应用,一个模块可以分成三个9位乘法器,将DSP模块的效率提高了三倍。一个精度可调模块能够高效的满足所有这些范围要求。从而支持设计人员让FPGA资源来适应其算法,而不是让算法来适应有限的资源要求。

本文引用地址://m.amcfsurvey.com/article/136063.htm硬核IP实现了高性能,提高了灵活性,而且缩短了设计时间

Altera在固定硅片中增强了某些常用的IP模块(例如,双倍数据速率存储器控制器、协议堆栈,甚至是嵌入式ARM处理器),释放宝贵的可编程逻辑资源,用于实现其他逻辑功能,从而提高了性能,降低了功耗和成本。作为一个例子,PCI Express®(PCIe®)协议堆栈需要大约150K LE作为软核实现,在硬核模块中则只需要三分之一的器件面积。采用竞争技术和工具尝试实现PCIe内核的用户会发现,使用Altera硬核IP结合Qsys系统集成工具,在设计和调试时间上平均能够节省6个星期的时间。这对于设计团队而言意味着大幅度降低了成本。

Altera还在FPGA中引入了第一种PCIe多功能支持。这一技术简化了不同外设之间对PCIe链路带宽的共享。支持8种功能,PCIe多功能支持将多个单一功能端点集成到一个多功能端点中。这缩短了开发时间,能够节省20K LE。

利用PCIe多功能,设计人员能够很好的定制业界标准处理器和驻留在FPGA逻辑中特有的多种外设。而且,支持多功能后,设计人员可以使用标准操作系统(OS)驱动软件,在FPGA的外设上共享PCIe链路带宽。没有多功能支持时,开发过程中的一项主要工作是定制驱动软件以实现这种资源共享功能。而且,多功能支持不需要多个软核或者硬核PCIe内核,将其集成到了一个多功能PCIe端点中,从而有效降低了成本。

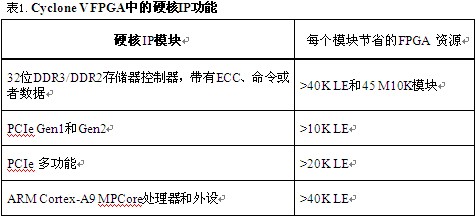

硬核IP最早出现在Altera的40-nm器件中,作为PHY层单元,因此,不再需要外部高性能串行I/O电路板元器件。在Altera 28-nm器件中,嵌入式硬核IP模块实现了ASIC的成本、性能和功耗特性,不会牺牲设计灵活性。例如,可以在Cyclone V GT器件中配置PCIe硬核IP模块来支持PCIe Gen1或者Gen2。此外,Cyclone V FPGA还提供两个硬核PCIe内核——是竞争器件的两倍。与软核逻辑实现相比更强的优势是,硬核IP模块功耗降低了65%,而性能提高了50%,表1列出了Cyclone V FPGA中的硬核IP功能,以及通过硬核实现所节省的资源量。

成熟可靠的收发器,针对各种数据速率进行了优化,缩短了调试时间

Altera的28-nm系列产品引入了模块化收发器,支持设计人员满足实际应用的器件性能需求。在Altera所有28-nms FPGA系列中,这种收发器使用了相同的基本体系结构,最大工作速率从3.125-Gbps直至28-Gbps。正如Stratix V和Arria V器件一样,Cyclone V收发器能够在几种不同的速率设置之间动态切换,可以降速来降低功耗。这种选择功能为降低系统平均功耗提供了一种方法,在空闲时,收发器工作在最小速率,根据需要切换到高速工作。

如果I/O扩展等应用只需要5-Gbps或者速率更低的收发器,那么,不会出现28-Gbps工作时大型晶体管那样的功耗和成本。相反,收发器以最低功耗和最低成本实现了3.125-Gbps和5-Gbps性能,Cyclone V FPGA系列能够很好的适应设计。与Stratix V和Arria V器件中的收发器相似,Cyclone V FPGA收发器支持多种协议,包括,3G SDI、千兆以太网(GbE)、CPRI、Display Port、PCIe、Serial ATA (SATA)和Serial RapidIO®等。Altera收发器信号完整性以及通过收发器工具包实现的实时调试功能,能够节省数星期的电路板开发和调试时间。

f 关于收发器工具包的详细信息,请参考Altera网站的收发器工具包页面。

仅采用两种电压轨,简化了电源分配,降低了成本

在所有低成本FPGA中,Cyclone V FPGA需要的电压轨数量最少。它们有内置片内电压稳压器,因此,您只需要使用两种电压轨来同时支持逻辑和收发器电源。这样,可以不需要板上电压稳压器,避免了布线拥塞,减少了所需的电路板层数,从而简化了电路板设计。竞争器件至少需要三种电压轨来支持内核、I/O和收发器逻辑。额外的电源轨需要增加元件以及PCB面积,还可能会带来布线拥塞问题,因此,在您的电路板开发预算中,成本可能会增加10到30美元。

fPLL可合成任意频率,不需要额外的振荡器

Altera 28-nm器件的通用锁相环是fPLL,它具有高级分段式频率合成以及M/N频率实现功能。在标准PLL中,M和N值都是整数。Altera采用了delta-sigma调制器,并在反馈通路中使用了32位M和N值,支持反馈M分频器采用分段值。这支持实现精确的频率合成功能。能够合成任意时钟频率,fPLL可以替代电路板上的振荡器,从而降低了电路板成本,减小了电路板面积。

智能引脚布局提高了可布线能力,缩短了调试时间

Cyclone V FPGA以最低的开发成本提供最好的信号完整性。采用了常规棋盘式电源和地模式,简化了布板。此外,器件左侧是常规的收发器布局,并进行重复,而接收器总是在外部,从而实现了最佳信号完整性。还尽量远离收发器放置存储器I/O引脚,相对于收发器进行屏蔽。Altera的方法是,首先通过避免引脚布局问题,减少在耗时的调试过程上的投入。

评论