基于DSP+ARM架构的协议转换器设计

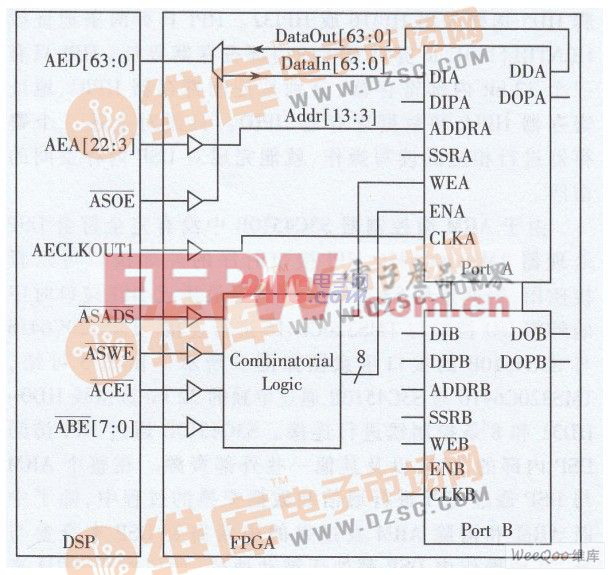

在该协议转换器中,DSP通过EMIFA接口连接到FPGA,实现DSP与FPGABlock RAM的无缝连接,从而使得DSP与FPGA之间的通信问题转化为DSP对其EMIFA外设的访问,达到了提高系统实时性的目的。为了保持FPGA与DSP之间的同步,FPGA的时钟直接由DSP内部的锁相环提供。DSP处理器TMS320C6416与FPGA的接口示意图如图2所示。

图2 TMS320C64l6与FPGA接口示意图

2.2 S3C451OB及其外围电路设计

ARM芯片选用Samsung公司的S3C4510B。S3C4510B是基于以太网应用的高性价比16/32 bit RISC微控制器,内含一个由ARM公司设计的16/32 bitARMTTDMI RISC处理器核。S3C4510B提供了一套比较完整的通用的外围设备,从而使得整个系统消耗最小。正是因为它具有很多常用的功能模块,所以也免去了添加配置附加设各的麻烦。芯片上集成的功能主要包括以下几个方面田:3.3 V ARM内核和3.3 V外部I/O,具有50 MHz时钟频率的微处理器;8 KB的Cache/SRAM;一个10/100 Mb/s以太网控制器,MII接口;2个HDLC通道,每个通道可支持10 Mb/s;2个UART通道,2个DMA通道,2个32 bit定时/计数器;1个通道IIC接口,18个可编程I/O口;中断控制器,支持21个中断源,包括4个外部中断;支持SDRAM、SRAM、Flash等;具有扩展外部总线和JTAG接口,支持软件开发及硬件调试。

本设计选用ARM微控制器S3C4510B是因其集成有以太网控制器和极强的外围扩展能力。S3C4510B以及其外围芯片Flash、SDRAM组成了整个系统的核心,负责控制和协调各模块工作,并实现与远程上位机的以太网通信。本设计对S3C4510B内部SDRAM和ROM进行了扩充。采用两片SDRAM芯片HY57V641620并联构建32 bit的SDRAM存储系统;采用一片Flash芯片HY29LV160构建16 bit的Flash存储器系统。

2.2.1 ARM与DSP的接口电路

由于ARM微控制器要实现整个系统的协调控制和网络功能,DSP处理器要执行复杂计算,因此需要实现ARM和DSP之间的数据交换。从某种程度上来说,ARM和DSP之间数据交换的速度决定了整个系统的运行速度和性能。

DSP处理器TMS320C6416集成了一个16/32 bit宽的主机接口HPI,HPI通过复位时的自举和器件配置引脚HD5选择采用HPI16或HPI32。UPI具有两条地址线HCNTRL[1:0],负责对HPI的内部寄存器寻址。HPI只有三个32 bit内部寄存器,分别是控制寄存器HPIC、地址寄存器HPIA和数据寄存器HPID。只需对上述三个寄存器进行相应的读写操作,就能完成对DSP内存空间的访问。

由于ARM微控制器S3C45l0B中没有完全符合DSP处理器TMS320C6416 HPI接口时序的外部接口可以直接使用,因此选用S3C4510B中时序最接近HPI接口时序的外部I/0接口与TMS320C6416进行连接。TMS320C6416与S3C4510B的接口示意图如图3所示。由图3可知,TMS320C6416与S3C4510B通过单独的32 bit数据线HD0~HD31和8条控制线进行连接。S3C4510B通过HPI访问DSP内部的RAM以及其他一些外部资源。在整个ARM与DSP通过HPI进行通信和数据交换的过程中,除了中断ARM和清除ARM发过来的中断需要DSP本身参与外,其他操作中DSP都处于被动地位。所以对于ARM来说,DSP就相当于一片外接的SDRAM。

评论