一种改进型的时分多址的实现方法

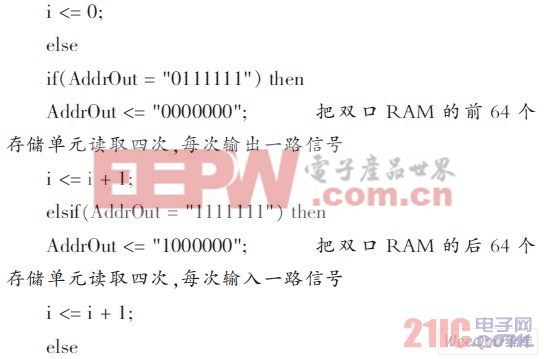

在端口B输入时钟elk12288的每个下降沿,端口B输入地址AddrOut都递增1,则在elk12288的上升沿,根据例化的双口RAM的IP核,相应的地址空间中的数据将通过Dout被读出来。本文引用地址://m.amcfsurvey.com/article/156579.htm

依次将输出数据以时分多址的帧格式传输出去。

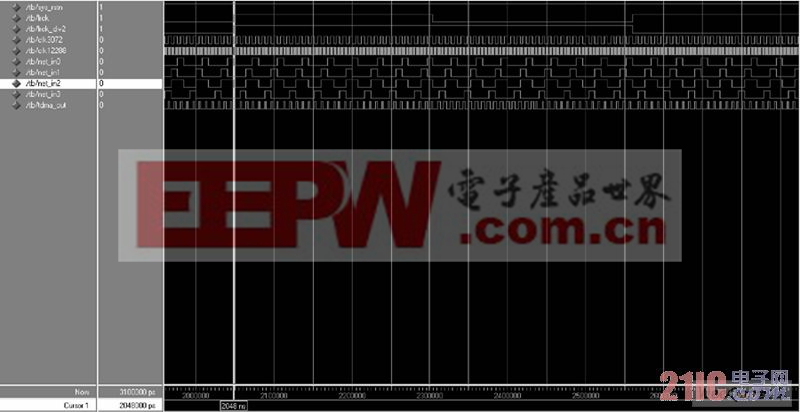

3 仿真结果

用ModelSim se 6.2b对程序进行仿真,在48 kHz的时钟周期内,给第1路输入源的64位输入信号为0x1111111111111111,第2路输入源的64位输入信号为0x2222222222222222,第3路输入源的64位输入信号为0x3333333333333333,第4路输入源的64位输入信号为0x4444444444 444444。仿真结果如图2所示。

图2 仿真结果

由仿真图可以看出,在一个48 kHz的时钟周期内,TDMA_OUT,即时分多址帧格式的输出为0x11111111111111112222222222222222333333 33333333334444444444444444,即每一帧被分成了4个时隙,4路输入信号在每一帧中占用各自的时隙进行传输,通过该仿真结果,可以验证该方法的可用性。

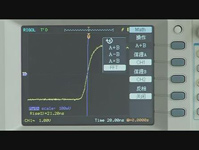

将VHDL语言程序通过ISE10.1综合,布局布线后,通过JTAG线缆下载到XC3S500E中进行电路板上的测试,再次验证了该方法的正确。

通过ISE综合后,可以看到程序所占用的芯片资源如下表所示。

表1 芯片资源情况

从表中的数据可以看出,通过使用一个BRAM从而节约了大量的资源,FPGA芯片资源的重要指标Slices仅仅占用了15个,LUTs仅仅用了29个,可见,该方法所占用的FPGA资源极少,达到了设计目标。

4 结论

本文研究了FPGA实现时分多址的一种改进型的方法,通过使用FPGA芯片内部的双口RAM,利用IP核,实现了多路信号转换成时分多址帧格式信号进行传输,根据所占资源的统计数据,可以看到在完成相同功能的前提下,该方法相比于已有的方法,确实能大量节省FPGA芯片的逻辑资源,从而使单片FPGA能完成更多的逻辑功能。但是,此方法会占用一部分双口RAM,在双口RAM资源紧张的时候不是太适用。

用ModelSim SE 6.2b对FPGA程序进行了仿真,并且将程序下载到电路板上进行了验证,证实了该方法的可用性。

评论