采用桥接方案还是纯PCIe方案

是否用桥的考虑因素

桥的加入可能增加也可能降低解决方案的性能。桥本身会引入延迟,因此会降低突发业务的吞吐量。不过,如果PCIe器件能够指定可预取的地址空间,那么利用预取可以提高吞吐量。这种技术一般只可用于嵌入式系统。表1总结了是否使用桥的一些关键考虑因素。

案例1:利用纯PCIe芯片构建SATA RAID存储控制器卡

SATA RAID控制器解决方案几年前就有了,最早采用的是32位PCI接口。随着SATA-2硬盘驱动器性能要求的不断提高,64位PCI-X接口现已非常普及。当PCIe推出后,服务器很快就转向PCIe,从而推动了同一RAID控制器的PCIe版本的迅速开发。一些RAID卡设计师插入PCI-X到 PCIe的桥,以此提供PCIe连接;也有的设计师采用纯PCIe的ASIC芯片设计新的RAID卡。还有些设计师两种方案都做,在基于桥的设计赢得一些早期用户的采纳后再实施纯PCIe方案。让我们分析一下后者,以便了解他们作出这种选择的根本原因。

案例1:利用纯PCIe芯片构建SATA RAID存储控制器卡

SATA RAID控制器解决方案几年前就有了,最早采用的是32位PCI接口。随着SATA-2硬盘驱动器性能要求的不断提高,64位PCI-X接口现已非常普及。当PCIe推出后,服务器很快就转向PCIe,从而推动了同一RAID控制器的PCIe版本的迅速开发。一些RAID卡设计师插入PCI-X到 PCIe的桥,以此提供PCIe连接;也有的设计师采用纯PCIe的ASIC芯片设计新的RAID卡。还有些设计师两种方案都做,在基于桥的设计赢得一些早期用户的采纳后再实施纯PCIe方案。让我们分析一下后者,以便了解他们作出这种选择的根本原因。

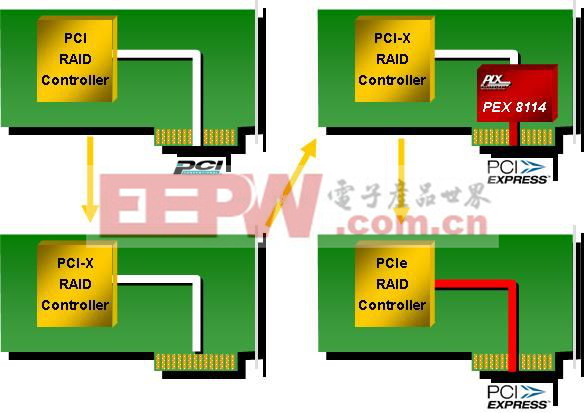

图1:SATA RAID控制器

在本案例中,基于PCI-X RAID芯片的板卡在市场上才面市不久,PCIe版的卡就有需求了。既然这是长期发展的必然趋势,而且SATA RAID功能又有足够大的需求量,因此就选择了开发ASIC,也就是开发需要花14个月时间进行设计和工艺变更才能实现的纯PCIe解决方案(见图1)。工艺技术之所以要改变是因为纯PCI-X的RAID控制器使用的0.18微米CMOS技术无法提供PCIe物理层(PHY)单元。由于新的PHY单元要求以及向更新工艺(0.13微米CMOS)的转变,ASIC实现似乎存在一定的风险。为了缩短TTM、降低芯片开发的风险,因此就有了“两条腿走路”的方案。这样可以快速部署基于桥的解决方案,从而满足早期用户的需求,一旦ASIC芯片通过认证,便可以推更低成本的纯PCIe方案了。

评论