四路低本底αβ测量仪电路设计

比较矩阵

本文引用地址://m.amcfsurvey.com/article/164393.htm比较矩阵对经过放大整形后的6路信号进行比较,把模拟幅度信息转换成数字脉冲信号,每路主探头的信号经过比较后生成3路数字脉冲信号(分别对应高、低β阈和α阈),6路信号经过比较矩阵后共生成14路数字脉冲信号(12路主信号和2路反符合信号)。

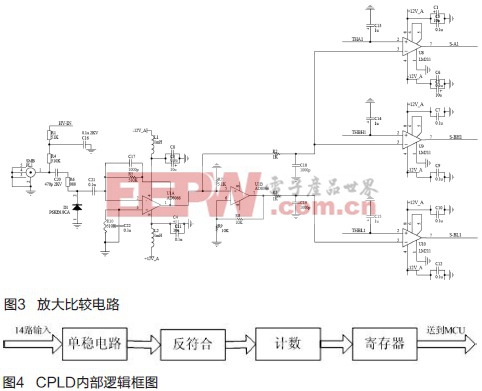

设计的比较矩阵由14个比较器组成,如图3所示。比较器选择高速比较器LM211,该比较器输出为OC输出,因此可同时实现电平的转换,直接输出到可编程逻辑器件CPLD进行反符合和计数,工作电压±12V,输出电压+3.3V。各路比较器的比较参考电压由数模转换器电路控制,数模转换器选择4路串行12位数模转换器DAC7554,工作电压+5.5V,输出电压范围0~5V,DAC7554通过SPI接口和MCU通信。

可编程逻辑器件CPLD

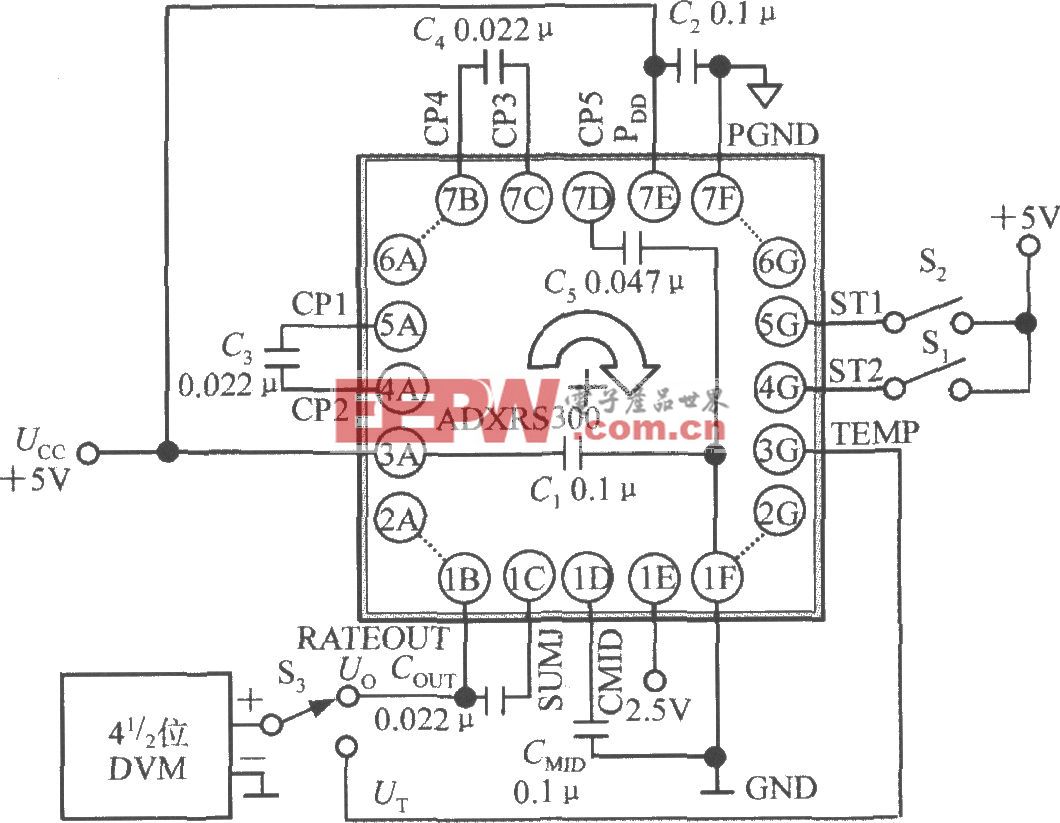

可编程逻辑器件CPLD实现反符合电路和计数电路,反符合电路对各路脉冲信号实现宽窄不同的单稳信号整形,把主探头信号转换成窄脉冲的主信号,把反符合探头信号转换成宽度为主信号两倍的反符合信号,以便于对主信号的反符合,消除由于主信号放大通道和反符合信号放大通道时间常数的差异引起的信号输出时间上的偏差,以实现反符合的准确有效。计数电路用于各路信号的计数和锁存,便于MCU读取。具体如图4所示。

可编程逻辑器件CPLD对比较矩阵的14路数字脉冲信号的进行反符合处理和α/β阈处理,产生8路(分别对应每路主探头的αβ信号)计数脉冲,再以8路计数脉冲作为计数器的时钟信号,进行计数处理,计数结果存放在8个寄存器(16位宽)中,MCU可以定时的读取。另外可编程逻辑器件CPLD还实现比较矩阵每路比较阈值的设置和高压模块的高压设置。CPLD采用Altera公司的MAXⅡ系列低功耗CPLD,型号为EPM570,144管脚封装,具有570个逻辑单元[4]。

微控制器MCU

MCU是仪器的控制中心,完成高压参数和比较阈值参数的配置以及测量数据的读取和发送,并接收主机送来的命令参数。

MCU采用最新的ARM CORTEX-M3内核的STM32单片机,型号为STM32103VBT6,主频为72MHz,128K字节FLASH,20K字节RAM,100管脚封装。该系列具有功耗低,处理能力强等特点[5]。STM32的SPI1和数模转换器DAC7554连接,采用软件片选信号;UART1实现和计算机的串口通信,同时实现BootLoader功能,用于程序下载;PortC和PortD与CPLD连接,PortC用作地址线,PortD用作数据线,设为开漏输出模式,在需要读取数据时,输出全置1,模拟实现数据总线功能,这样不需要在输入输出时进行端口模式切换,提高了效率和可靠性。

单片机固件开发采用嵌入式操作系统,将整个系统划分为三个并行存在的任务层,按其优先级从高到低顺序排列依次是:数据采集计算任务、串口通讯任务、状态显示任务等,嵌入式操作系统按优先权的高低对各任务进行任务调度。

电路相关文章:电路分析基础

比较器相关文章:比较器工作原理

电荷放大器相关文章:电荷放大器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论