基于TMS320DM642 的X264 视频编码器的优化

下面举一个SAD_4×4 的例子来说明上述各项是如何实现的。SAD_4×4 的C 语言版本的代码为:

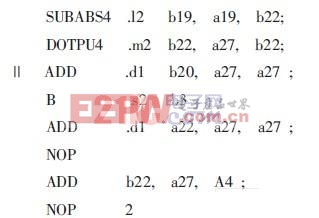

SAD_4×4 的汇编语言版本的代码为:

完成汇编指令的编写后,进行汇编语言的调试。由于X264 工程比较大,如果直接在工程中调试,难度较大,所以在调试过程中建立一个小工程, 从文件中读出一段数据来测试汇编语言功能的正确性。具体的步骤是:采用单步调试的同时, 开启调试器CCS 里面的view memory 和view core registers 选项来观察相应的memory 和寄存器里面的值是否按照逻辑设计进行改变。如果结果不对,则考虑是否错误地使用了寄存器, 或者是没有等待足够多的延时周期, 或者是出于软件流水的目的错误地安排了指令的顺序,直到找出错误的地方。

4 小结

笔者首先分析了从PC 平台移植到DSP平台后的X264 编码工程,其编码速率低,满足不了视频压缩实时性要求。接着从提高编码器的编码速度角度出发,对编码工程进行了优化,介绍了在实际中用到的几种DSP平台优化方法:算法与程序系统结构的优化,EDMA 与乒乓缓存优化,循环体的优化,编译器优化和DSP汇编。对CIF格式图像采用BASE_LINE 进行编码, 优化前X264 编码速度约为5~8 f/s(帧/秒),优化后的编码速度为20 f/s 左右,速度得到明显提升,基本能够实现实时编码。本文引用地址://m.amcfsurvey.com/article/166324.htm

评论