基于MSP430单片机的智能阻抗测量仪设计

2 系统硬件设计

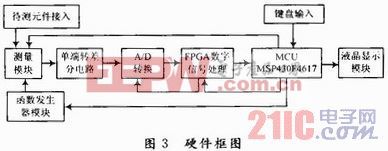

测量仪的硬件由MCU模块、FPGA数据处理模块、A/D采样模块、单端转差分模块、测量接入模块、函数发生器模块、键盘模块、液晶显示模块构成,硬件框图如图3所示。本文引用地址://m.amcfsurvey.com/article/171157.htm

2.1 系统主控制MCU模块

仪器的控制核心采用MSP430F4617单片机,该芯片有2个16位定时模块单元,多路12位A/D采样转换模块,12位D/A转换模块,多路时钟系统,存储容量大,数量多的I/O口,在整个系统中是利用率比较高的器件。在系统测量过程中,首先用于分析测量数据,根据测量值与没定参数比较,然后再反馈给控制测量模块选择合适R0达到最佳测量状态。根据初步测量结果反馈控制函数发生器以及内部定时器选择合适函数频率,进行精确的测量,最终控制液晶显示器将测量的元件的电学特性RLC值输出显示。

2.2 FPGA数字信号处理模块

FPGA芯片采用XC3S200A芯片,系统中高速A/D采样芯片工作频率较高它的控制时钟以及采样时序主要由FPGA控制产生,同时利用FPGA处理数字信号速度快的特点对图3两路信号V0,Vx进行FFT运算分离出实部虚部信息,并将数据传送给单片机。

2.3 A/D采样模块

为了减小图3中2个模拟输入信号V0,Vx的相位误差,系统采用AD7862高速、低功耗、双核12位模数转换器(ADC)芯片进行采样。该器件内置2个4μs逐次逼近型A/D转换器、两个采样保持放大器、一个2.5 V内部基准电压源和一个高速并行接口,它有4个模拟输入组成2个通道A和B(分别用于采样V0、Vx信号),每个通道的两个输入(VA1与VA2或VB1与VB2)可同时进行采样和转换,通过A0(FPGA控制)作为输入选择通道,采样时序由FPGA提供。

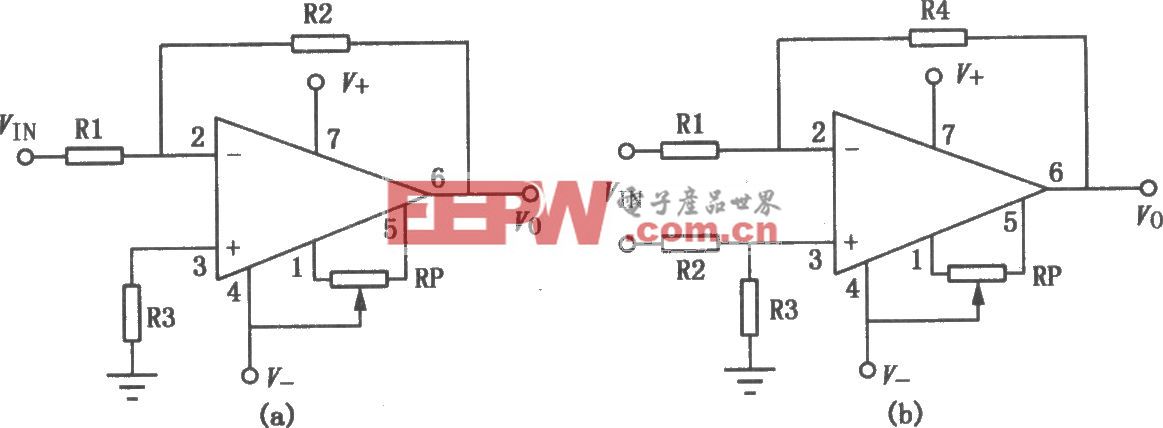

2.4 单端转差分电路

后级A/D采样电路需要在差分输入状态下达到最佳采样精度,所以需要将前级测量模块产生的V0,Vx差分化预处理,这里采用全差动运算放大器THS4503进行转换,THS4503具有非常卓越的线性度,输出模式可调,电压工作范围宽(5V,5V,12V,15V)工作带宽可达370MHz,转换速度极快达到2 800 V/s。另外,还需要REF2330芯片为THS4503以及A/D采样模块提供基准电压。

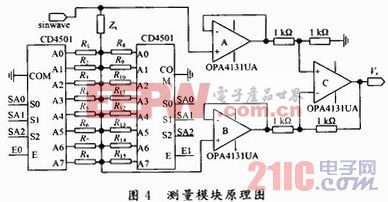

2.5 测量模块

测量模块是待测元件与标准R0分压部分,主要包括减法电路求Vx、减法求V0电路以及标准电阻R0选择电路,如图4所示。由于图2中的Vx不便直接测量,所以通过减法电路来求Vx。当图4减法电路求得Vx的同时,也引入了新的环境变量,因此,使V0也通过相同的电路环境以减小系统误差。可以分析得出,当图1中Vx/V0为1:1时测量精度最高,所以需要调整R0与待测元件的分压接近1:1来保证测量精度。标准电阻R0

由MSP430单片机控制的模拟开关CD4051进行软件选择。

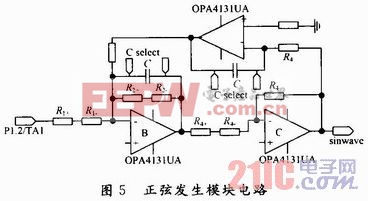

2.6 函数发生器模块

在图1测量原理中,测量是工作在正弦信号的条件下,要保证测量的精度,测量频率必须保证相当稳定。所以,利用晶体振荡器振荡频率稳定性高的特点来获得测量频率将很好的保证我们测量的稳定性。同时利用单片机定时器分频晶振产生的频率,可以获得频率稳定性高的各种频率。单片机的定时器输出为方波信号,要获得正弦信号,需要对方波信号进行滤波,将方波的中心频率信号滤出并保证相当的信号强度,因此需要设计一款性能良好的滤波器。此外,设计的滤波器必须有较高的Q值以提高选频特性。其电路原理如图5所示。

评论