基于ARM的高精度数据采集系统设计

3 抗干扰设计

A/D转换过程中,会遇到被采集信号小而干扰噪声强的情况,干扰有来自器件温度变化、接触电阻、引线电感、接地和电源等。因此,在整个数据采集系统设计中,要特别注意抗干扰的设计,根据具体的采集系统,本方案中主要考虑了以下几方面:

(1)合理设计印制板:根据硬件功能进行模块化布局,数字部分和模拟部分要分开,使用多层板,电源层和地层相互独立,电源线和地线要相对加粗;合理走线,避免信号线与高频线近距离平行走线。

(2)电源设计方面:在设计每个芯片的供电电路时,在每个芯片的电源附近并联去耦电容和旁路电容。

去耦电容为芯片提供局域化的直流,旁路电容可以消除高频辐射噪声和抑制高频干扰。

(3)接地方面:模拟地和数字地应严格分开,最后单点共地。共地点选择在ADC芯片管脚所需电流最大的位置,这样可以使大电流对地回流最近,以避免对模拟电路的干扰,提高系统的采集精度。模拟地和数字地可以通过磁珠连接,由于磁珠的高频阻抗大,而直流电阻为零,能够滤除高频电流减少地线上的高频噪声。

(4)防止空间电磁辐射对系统的干扰:由金属材料做成屏蔽罩,将器件屏蔽起来,并将屏蔽罩妥善接地。

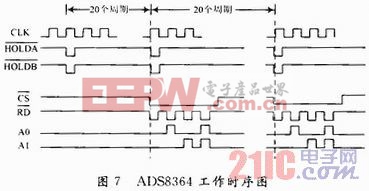

4数据采集的时序控制

对该A/D芯片CLK的要求为小于5 MHz即可,本方案结合ARM的处理能力,选用1 MHz的时钟,A/D芯片每20个时钟周期完成一次转换,采集率为50kHz。时钟信号CLK可以一直输出。CLK为上升沿触发。芯片上电后,首先进行复位操作,将![]() 置为低电平并保持宽度50ns以上,之后一直将RST置为高电平。

置为低电平并保持宽度50ns以上,之后一直将RST置为高电平。![]() ,

,![]() 平时一直为高电平,当需要采集的时候,将

平时一直为高电平,当需要采集的时候,将![]() 同时置为低电平,并将

同时置为低电平,并将![]() 保持时间为50 ns到半个时钟周期的宽度,之后

保持时间为50 ns到半个时钟周期的宽度,之后![]() 信号恢复到高电平。此时完成输入端信号的锁存。经过20个时钟周期后,4个通道都已完成模/数转换,并把转换结果放在输出端对应的寄存器内。下一步要做的就是把寄存器内的数依次取出,读进单片机里。将

信号恢复到高电平。此时完成输入端信号的锁存。经过20个时钟周期后,4个通道都已完成模/数转换,并把转换结果放在输出端对应的寄存器内。下一步要做的就是把寄存器内的数依次取出,读进单片机里。将![]() 置为低电平,将

置为低电平,将![]() 置为低电平,并将AO,A1,A2同时置为0,0,0,之后经过40 ns后,通道1的数据便放到了16位数据总线上。单片机可以进行读取。的宽度可以和时钟一样,当变为高电平时,单片机读取16位数据总线上1通道的转换结果。随后

置为低电平,并将AO,A1,A2同时置为0,0,0,之后经过40 ns后,通道1的数据便放到了16位数据总线上。单片机可以进行读取。的宽度可以和时钟一样,当变为高电平时,单片机读取16位数据总线上1通道的转换结果。随后![]() 变为低电平,并将A0,A1,A2同时置为0、0、1,之后经过40 ns后,通道2的数据便放到了16位数据总线上,随后在为高电平时将数据总线上的2通道的数据读走。然后依次时序继续读取通道3和通道4的数据。4个通道的时序都读取结束后,将

变为低电平,并将A0,A1,A2同时置为0、0、1,之后经过40 ns后,通道2的数据便放到了16位数据总线上,随后在为高电平时将数据总线上的2通道的数据读走。然后依次时序继续读取通道3和通道4的数据。4个通道的时序都读取结束后,将![]() 置为高电平,将

置为高电平,将![]() 置为高电平。工作时序图如图7所示。

置为高电平。工作时序图如图7所示。

5 结语

本系统设计以低功耗、小尺寸、低成本和高精度为目标。介绍系统时钟电路设计、ADC单元设计、电源设计、抗干扰设计及数据采集的控制时序设计。设计的难点在于高精度并行A/D采集模块与ARM芯片的通信及时序控制问题。调试结果表明该方案工作性能强,体积小,成本低,非常适用于小型化、低成本的数据采集领域。

评论