数模转换芯片AD9772A的特点及其应用

1 AD9772A内部结构

1.1 时钟产生和控制模块

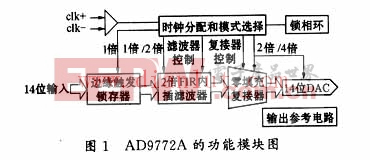

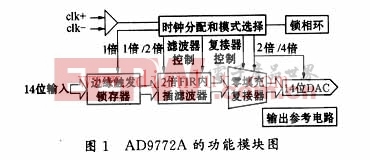

AD9772A内部模块依据功能可以划分为:时钟产生和控制模块,输入锁存模块,内插滤波模块,“零填充”模块,数模转换模块以及输出参考电路。图1是AD9772A的功能模块图。

时钟产生和控制模块使用锁相环实现,主要为片内各个功能模块提供时钟和控制信号,环路

的参数直接决定了数模转换的性能。时钟产生和控制模块由差分输入,相位检测,环路滤波(外围电路配置),压控振荡器(VCO),分频器和时钟分配模块组成。

依据输入数据速率,锁相环路有两种工作模式:当输入数据速率大于6 MSPS时,锁相环路工作,相应的管脚PLLVDD=Vcc,PLLCOM=gnd;当数据速率小于6 MSPS时,为了获得更高的相噪性能,不使用内部的锁相环路,相应的管脚PLLVDD=PLLCOM=gnd。

无“零填充”时,参考时钟是输入数据速率的2倍;有“零填充”时,参考时钟是输入数据速率的4倍。对于QPSK调制来说,当使用内部锁相环时,锁相环路本身可以保证2个AD9772A芯片时钟和数据同步;不使用内部锁相环时,通过复位管脚(RESET),能够实现2个AD9772A芯片时钟和数据同步。

锁相环典型的开机锁定时间是100 ms。

时钟产生和控制模块的环路滤波器和压控振荡器模块由PLLVDD管脚统一供电,时钟差分输入、相位检测、分频器和时钟分配模块由CLKVDD管脚统一供电,为了确保最优的环路相位噪声性能,在设计电路时,要保证PLLVDD和CLKVDD来自相同的“干净的”模拟电源。是否使用片内锁相环,可以通过配置PLLVDD管脚实现,当使用内部锁相环路时,PLLLOCK表征环路是否锁定的信号,PLLLOCK电平为高,环路锁定;PLLLOCK电平处于高和低之间时,环路未锁定。当禁止内部锁相环路时,PLLLOCK提供了1倍内部时钟输出。

根据输入数据速率,分频器和时钟分配模块的控制管脚配置如表1所示。

1.2内插滤波器

AD9772A内插滤波器是在两个原始抽样点之间插入1个零值,然后通过一个FIR滤波器,插入的零点就可以还原为准确的内插值,提高了时域分辨率〔1〕。内插后的信号频谱为原始离散序列谱经2倍压缩后得到的谱,但是得到的频谱包含了有效频谱的高频镜像,根据AD9772A的应用环境,合适地选择低频频谱或高频镜像。如果保留高频镜像,输出信号频率提高了2倍,频谱结构没有变化,起到了上变频的作用。

AD9772A的FIR滤波器采用43阶对称滤波器实现,阻带可以达到73 dB的衰减。如果系统需要在宽带内获得更高的动态范围,AD9772A必须工作在基带方式下,相应的管脚MOD0=gnd,FIR内插滤波器表现为低通特性,输入数据频谱到第一个镜像频谱的距离增加,有利于模拟低通滤波器的设计。基带模式下使用“零填充”,相应的管脚MOD1=Vcc,虽然频谱的通带更加平坦,但是无杂散动态范围(SFDR)减小,阻带抑制不够,信噪比(SNR)减小。AD9772A工作在中频模式下时,MOD0=Vcc,FIR内插滤波器表现为高通特性,当中频超过输入数据速率,必须使用“零填充”,增加通带的范围。

输入时钟经过信号产生和控制模块送给各个功能子模块,输入数据经过一级锁存,进入2倍内插滤波器和“零填充”,增加了DAC的更新速度,使后继电路容易设计,内插和填充后的数据送入模数转换器,完成数字信号到模拟信号的变换。

2 AD9772A在WCDMA发送电路中的应用

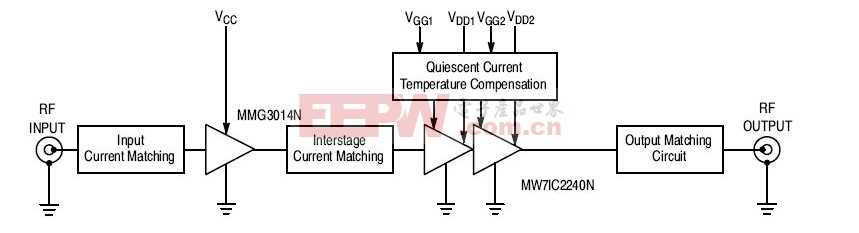

WCDMA(宽带码分多址)系统基站发送物理信道多,数据动态范围较大,AD9772A提供了14位输入管脚、0.1dB的带内波动、73dB的带外衰减和高达74dB的SFDR,通过与模拟低通滤波器的配合,能够获得失真和噪声性能很好的基带模拟信号,可以满足基带发射性能指标。AD9772A应用时,应该从系统的角度设计AD9772A的参数,这些参数包括:输入数据速率、时钟频率、复位信号、锁相环路、模式配置、分频比和参考电阻等。图4是WCDMA基站部分发送电路功能框图。

2.1 电路设计

为了获得“干净”的基带信号,做印刷电路板(PCB)时,模拟电路部分和数字电路部分尽量集中,不能交叉布线。而AD9772A输入是数字信号,输出是模拟信号,芯片中同时存在数字电压、数字地、模拟电压和模拟地,芯片各个功能模块由不同电源供电,对这些信号处理时,要遵循以下原则:片内锁相环路工作时,PLLVDD=CLKVDD=3.1V~3.5V;DVDD1-2=CLKVDD

评论