一种新型的交流电源信号发生器的设计

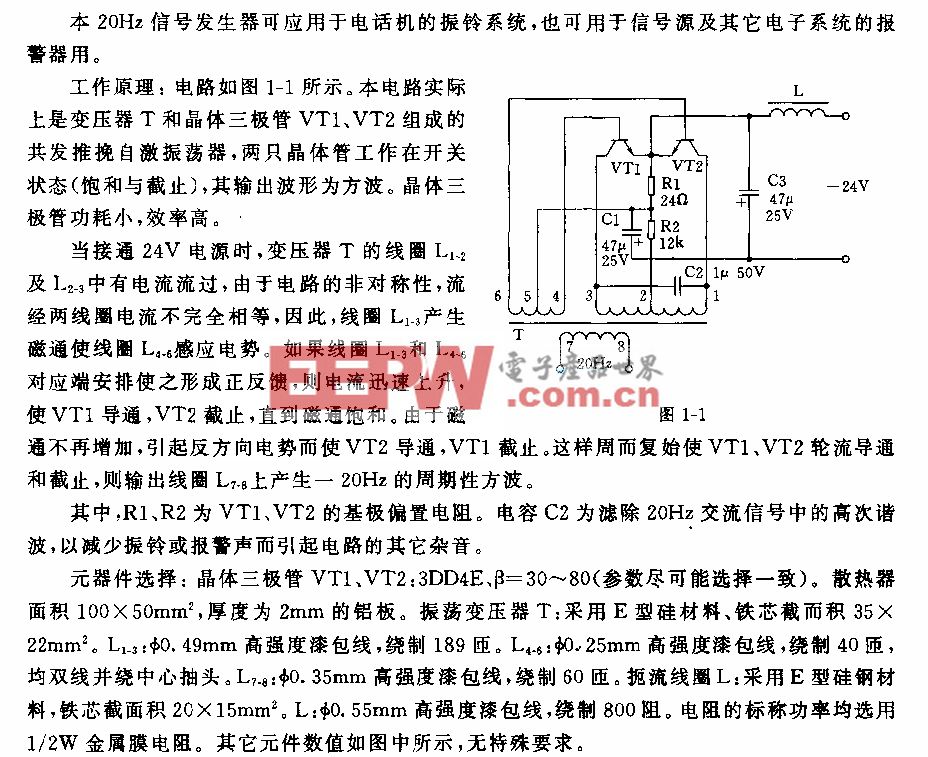

(2)应用CPLD设计交流电源信号发生器

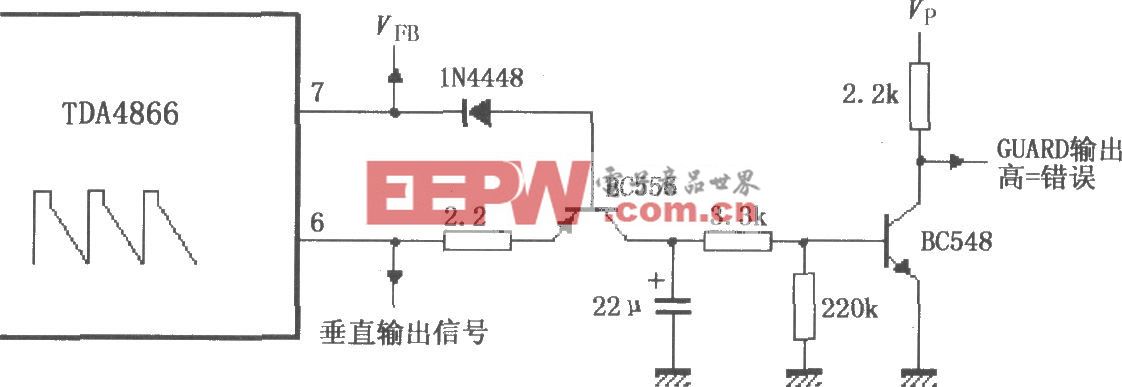

基于CPLD设计交流电源信号发生器,采用有源晶振16.384 MHz作为频率参考,设计分频器进行32分频,分频信号通过计数器再2分频同时占空比调整为50%,即可得到256 kHz信号1输出;信号1通过计数器再16分频,即可得到16 kHz信号2输出;信号2通过计数器再2分频,即可得到8 kHz信号3输出;同样的道理可以得到4KHz信号4输出、2 kHz信号5输出。电路实现框图如图3所示。本文引用地址://m.amcfsurvey.com/article/175951.htm

电路要求1 kHz三相120°输出,需要先得到6kHz频率,后再6次分频每次分频三相有对应的电平输出。基准频率16.384 MHz分频2731次可以得到5.999 kHz,再6分频可到0.9998779 kHz,频率精度理论值为1.2x10-4,电路实现框图如图4所示。

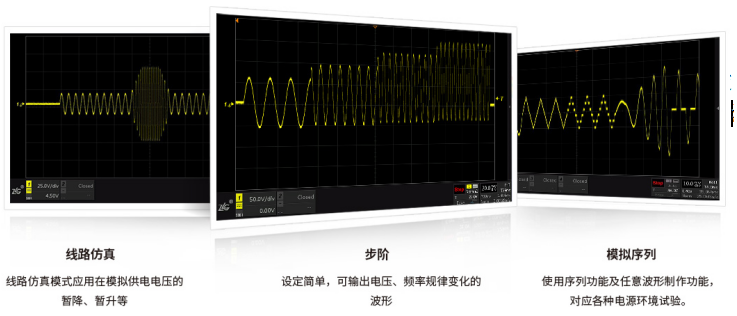

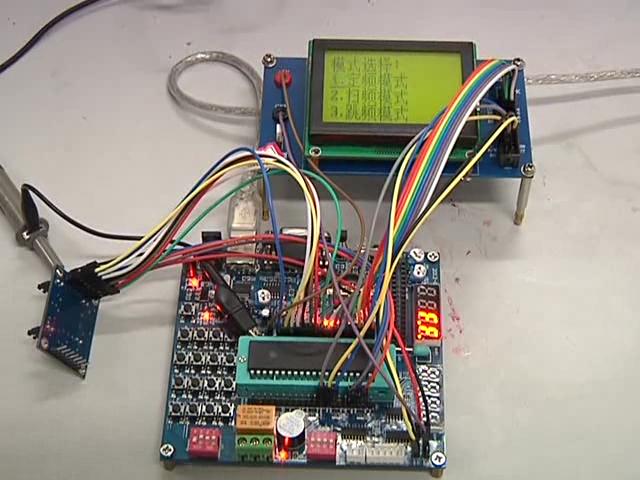

(3)仿真及实验结果

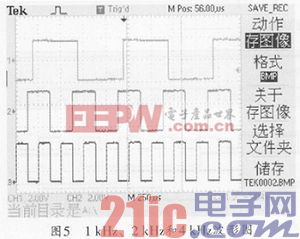

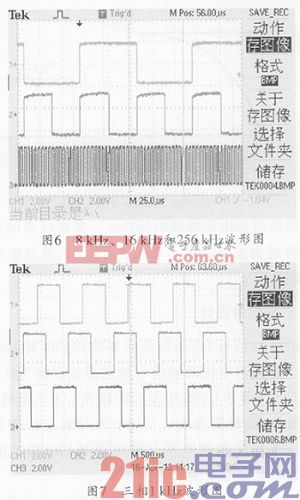

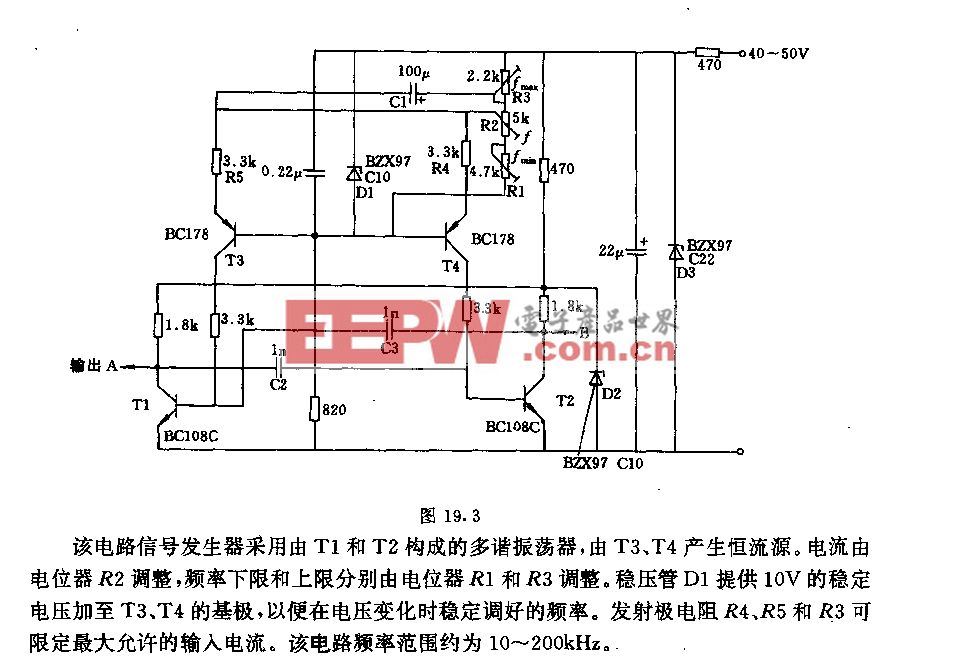

1 kHz、2 kHz和4 kHz实验波形如图5所示,8kHz、16 kHz和256 kHz实验波形如图6所示,三相1kHz波形如图7所示。

从图7可以看出三路输出信号相位相差120°,频率为999.875 Hz频率精度为1.25x 10-4。

评论