8位1.0GSPS ADC芯片MXT2001原理与应用

(1)OUTV/SCLK:输出电压幅度和串行接口时钟。为高电平时,表示正常差分输出数据幅度,为低电平时,表示降低差分输出幅度和降低功耗。当扩展控制模式被激活,SCLK作为串行数据的输入时钟。

本文引用地址://m.amcfsurvey.com/article/185192.htm(2)OUTEDGE/DDR/SDIN:DCLK边沿选择,双数据速率(DDR)和串行数据串行输入。当输出数据转换时,此引脚设定DCLKp的输出边缘。当引脚浮空或连接到1/2电源电压时,使能DDR时钟。在扩展控制模式下,此引脚作为串行数据输入端(SDIN)。

(3)RESET:复位。当引脚输入正脉冲用于复位和同步多个转换器的时序DCLK。

(4)PD/PDQ:低功耗掉电模式。PD引脚为高电平时,芯片进入低功耗掉电模式。当PDQ引脚接高电平时,只有Q通道进入低功耗掉电模式。

(5)CAL:校准模式启动信号。最低80个时钟周期的逻辑低电平输入之后紧随80个时钟周期的逻辑高电平输入,将激发电路进入自动校准模式。

(6)FSR/ECE:全量程选择以及扩展控制模式选择,在非扩展控制模式,逻辑低电平会把全量程差分输入范围(峰峰值)设置为650mV;逻辑高电平会把全量程差分输入范围(峰峰值)设置为870mV。当此脚连接到1/2电源电压或者悬空时,进入扩展控制模式。

(7)CLKp/CLKn:ADC的LVDS时钟输入。这个差分时钟信号必须是交流耦合的。输入信号将在CLKp的下降沿被采样。

(8)VINIp/VINIn/VINQp/VINQn:ADC的模拟输入脚。

(9)CalFlag:校准运行指示。高电平有效。

(10)DI/DQ/DId/DQd:I通道和Q通道的LVDS数据输出。

(11)ORp/ORn:输入溢出指示。

(12)DCLKp/DCLKn:差分时钟输出,用于锁存输出数据。这些引脚可以选择延时或不延时以便输出同步,在单倍数据率SDR模式下,这些信号的速度为输入时钟的1/2,在双倍数据率DDR模式下,这些信号的速度为输入时钟的1/4。在校准周期内DCLK不被激活。

MXT2001的应用

MXT2001模数转换器可用于单/双通道的高速数据采集系统中,图3为该芯片工作于双通道采样模式下的典型应用原理图,外部I/Q双通道数据经此芯片进行模数转换,并通过LVDS接口电路输出并存储到FPGA芯片中。

MXT2001的管脚1至管脚36为输入管脚,其简化连接关系如图3所示。电路的典型工作条件为电源电压1.8V,时钟输入频率为1.0GHz,REXT脚接精度为0.1%,阻值为3.3kΩ的电阻,此电阻值将辅助设定芯片内部基准电流,应保证足够的精度(精度最好不要低于1%)。

该ADC的模拟信号输入(包括时钟输入和I/Q路信号输入),推荐采用差分输入而不是单端输入,这对系统的性能影响很大。如果被采样输入信号是单端信号,可以预先通过单/双端变换电路,将单端信号变成差分信号。采用BALUN(非平衡变压器,如型号ETC1-1-13)或者采用平衡电桥电路均可实现单端输入到双端输入的信号变换。

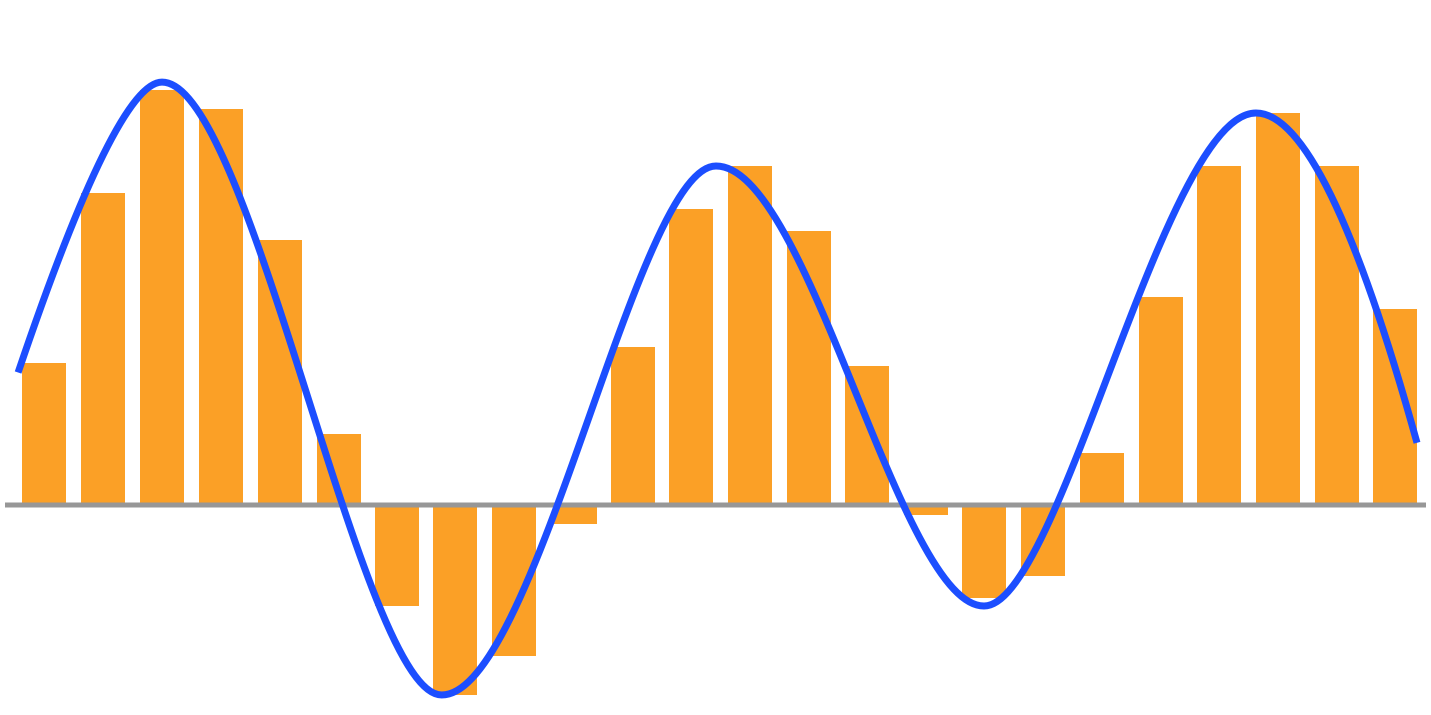

MXT2001输出的二进制编码数据为4路8位500Msps LVDS信号,可并行输入到FPGA芯片并转换成编码数字信号,转存在FPGA的FIFO存储体中,方便信号读取。采用的FPGA芯片可选择Xilinx公司的Virtex-4/Virtex-5系列产品,这类芯片的I/O管脚采用了片上同步(Chip-Sync)技术,便于高速采集数据的信号捕捉。

结束语

该款双通道8位1GSPS的ADC芯片MXT2001具有高速、高精度、低功耗、多通道的特点,具有优异的动态性能,可以广泛用于各种实时性要求特别高的军民用电子系统和测试设备中,为射频信号接收器,高速雷达,卫星机顶盒,通信系统,数字示波器,测试设备等高精尖设备提供关键器件。

模数转换器相关文章:模数转换器工作原理

评论