一种1.9V供电、8位3.0GSPS A/D转换器设计

数字校准技术

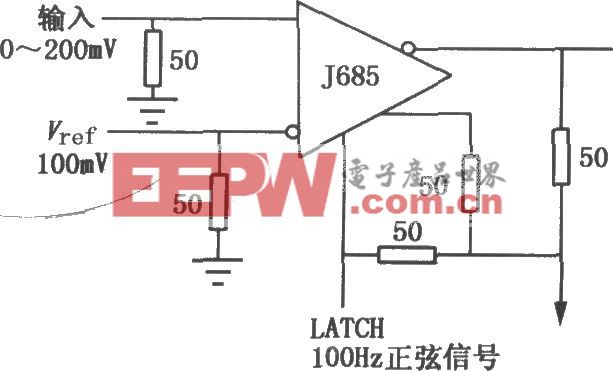

本文引用地址://m.amcfsurvey.com/article/185193.htm数字校准技术的应用可以使得在进行超高速A/D转换器设计时,着重注意A/D转换器的速度性能提高,打破按器件匹配进行设计的传统方式。在进行A/D转换器设计时,可以选用更有利于发挥A/D转换器速度优势的器件,将进行失调校正、精度优化的工作由数字校准技术完成。对于超高速折叠内插A/D转换器而言,在选择校准方法时,首先要考虑到其校准的速度要求,在优先保证高速度的前提下,再考虑其精度。因此,本文中的超高速折叠内插A/D转换器采用了前台数字校准方法,结构如图5所示。

其工作过程如下:校准电阻串采用N组间隔均匀的校准矢量电压VCAL,为N个直流电平。输入MUX模拟开关电路为二选一电路,在正常模式下选择外部信号输入,在校准模式下选择矢量电压VCAL输入。校准逻辑模块对校准模块进行逻辑控制和时序控制。可加/可减计数器是校准电路的运算核心,产生的数值将作为电流DAC的码位,并产生对应的调整电流。ADC模块的比较器产生输出信号,这个输入信号作为ADC模块的反馈在校准部分输入,通过对于反馈信号的判断,调整接口DAC的电流大小,从而使得A/D转换器的误差得到补偿,实现电路的校准。由于校准矢量信号依次通过了采保电路和转换电路,故整个模拟通道都得到了校准。

仿真结果

单元电路模块在Spectre仿真条件下进行设计仿真,包括电压拉偏、温度拉偏以及工艺角拉偏仿真等;整体电路的前仿及后仿则全部采用快仿工具完成仿真。转换器电路主要技术指标的仿真结果汇总见表1。

流片及测试结果

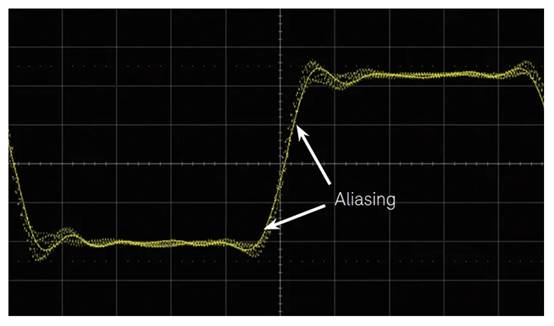

本文设计的8位3.0GSPS A/D转换器晶体管总数约为70万个,整体版图面积约为4.10×4.05mm2,采用0.18μm CMOS工艺流片,选用LQFP144封装,电路照片见图6。图7、图8和图9分别给出了转换器样片典型应用条件下的DNL、INL以及输入为747.390906MHz正弦波信号时的频谱分析结果。从图中可以看出,本文设计的8位3.0GSPS A/D转换器︱DNL︱最大值为0.22LSB,︱INL︱最大值为0.32LSB,常温条件下转换器的有效位为6.95Bits、信噪比达44.10dB、信噪谐波失真比为43.57dB、总谐波失真为-52.68dB、无杂散动态范围为51.18dB,测试指标全部达到或接近仿真结果。

比较器相关文章:比较器工作原理

评论