采用静态CMOS和单相能量回收电路的乘法器电路设计

本文引用地址://m.amcfsurvey.com/article/186047.htm

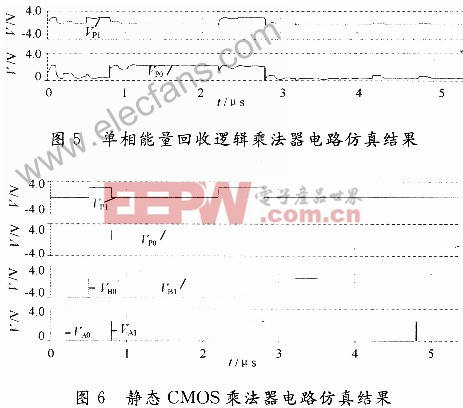

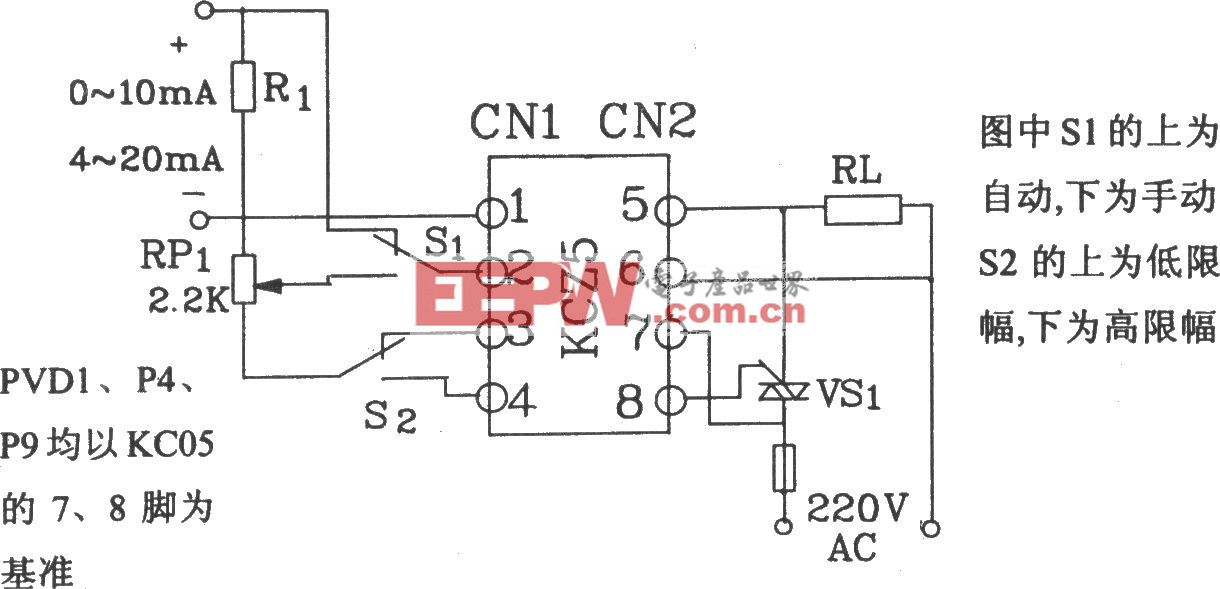

从图中可见,用静态CMOS电路构成的乘法器输出比较稳定,输出等于0或VDD,功率消耗为1.51×10-7W。而用单相能量回收电路构成的二位乘法器的输出不够稳定,对噪声信号较为敏感,但是并不影响输出逻辑,功率消耗减小为1.17×10-7W。从节能的角度来看,单相能量回收电路性能更好。

3 结语

本文首先介绍了单相能量回收反相器电路,详细讨论电路的工作原理,同时用PSpice工具仿真了基于静态CMOS电路和单相能量回收电路构成的两位乘法器电路。仿真结果表明本文介绍的单相能量回收电路能够极大地降低电路功耗。今后的工作还应继续优化电路结构,稳定电路的输出状态,增强电路的抗干扰能力。

p2p机相关文章:p2p原理

评论