基于Matlab的FIR带通滤波器设计及DSP实现

3FIR数字带通滤波器语音去噪的DSP实现

3.1 硬件结构

图3为FIR带通滤波器的语音去噪硬件结构框图。系统主要由DSP芯片(TMS320C5402)、A/D转换器(ADS7864)和D/A转换器(DAC7625)组成。本文引用地址://m.amcfsurvey.com/article/186064.htm

实现的核心器件采用TI公司生产的TMS320C5402芯片。该芯片采用先进的修正哈佛结构,片内共有8条总线、CPU、在片存储器、在片外围电路等硬件和高度专业化的指令系统,使它的处理速度和容量大大提高,为数字滤波中的复杂算法的实现提供了良好的保证。

A/D转换器采用TI公司生产的ADS7864芯片,它是一个高速(转换时间2μs)12位精度,6通道的A/D转换器件。它的最高工作频率可达8 MHz,采样率为500 kHz。根据奈奎斯特定理,信号的最高频率不能高于250 kHz,这样才不会有失真,而这个频率对于语音信号的处理已经足够。

D/A转换芯片采用DAC7625,它是一个4路12位D/A转换器件,每路都有输入寄存器和DAC寄存器,构成双缓冲结构,转换时间为10μs。

3.2 软件设计

3.2.1 数据组织方式

若输入信号x(n)和滤波器的单位冲激响应h(n)在频域分别为![]() ,则其输出信号的频率响应为

,则其输出信号的频率响应为![]() 。根据离散傅氏变换的性质,可以得到滤波系统的差分方程:

。根据离散傅氏变换的性质,可以得到滤波系统的差分方程:![]()

从上文Matlab的仿真过程可得到滤波器的级数N和滤波器系数h(n)。从上述可知数字滤波器实现时,主要是进行乘和加运算以及数据存取操作。

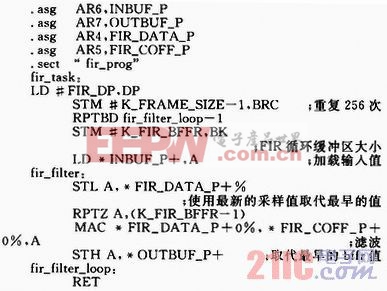

在定点DSP上实现FIR滤波有两种方式:一种是用线性缓冲区实现z-1,该方式能保证新老数据在存储器中的存放位置直接明了,新的数据存放在缓冲区的固定位置;另一种方式是循环缓冲区实现z-1,该方式新老数据在缓冲区的位置不直接明了,新的数据没有固定位置,但可以方便地完成滤波器窗口的自动更新。考虑到本方案中使用的是汇编语言编程,还有N的阶数较大,为提高速率,因此在选择FIR滤波器的方式时选择循环缓冲区实现z-1的方式。

对于N级的FIR滤波器,在数据存储器中开辟一个称之为滑窗的N个单元的缓冲区,滑窗中存放最新的N个输入样本。每次输入新的样本时,一新样本改滑窗中的最老数据,而滑窗中的其他数据不需要移动。利用片内BK(循环缓冲区长度)寄存器对滑窗进行间接寻址,环缓冲区地址首位相邻。

3.2.2 程序设计思路

程序设计的总体思路是:启动ADS7864对输入的模拟信号进行A/D转换,每采集到一个数据就送入DSP进行滤波运算,运算结果送DAC76 25转换为模拟量。不断地重复上述过程,在DAC7625的输出端就得到滤波后的模拟信号。

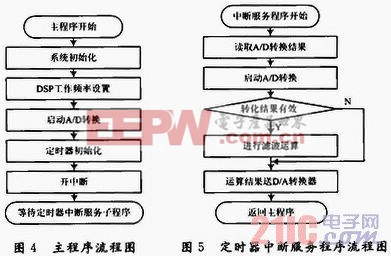

为了精确地控制ADS7864的采样率,使用TMS320C5402内部的定时器控制采样时间间隔T。设置定时器的定时时间等于采样时间间隔T,并让它工作在中断方式,则定时器每过T时间间隔就向CPU发出中断请求,CPU响应中断请求,转去执行中断服务程序。在中断服务程序中读取A/D转换结果,对转换结果进行滤波运算,并将运算结果送D/A转换器转换为模拟量。因此,程序分为主程序和定时器中断服务程序两部分,流程图如图4,图5所示。

3.2.3 FIR滤波源程序

FIR滤波器指令,使用MAC指令执行FIR滤波,将滤波输出放在累加器A中:

评论