一种带有增益提高技术的高速CMOS运算放大器设计

增益提高辅助运放也采用了两个全差分折叠式共源共栅结构,既可以减少电路的面积和功耗,又减少电路内部节点的电容。在辅助运放Ao的输出端添加两个补偿电容C0和C1,用以消除在主运放单位增益带宽附近产生的零极点对其中,由于Ao必须工作在较高的共模电压下,故选择NMOS管作为运放的差分输入管,相反,Ao是以PMOS作为差分输入管。以Ao为例,如图4所示,NMOS输入管接M9、M10的漏极,经过放大后输出到M7和M8的栅极,Ao只需提供M7,M8饱和工作所需的共模电平,因而不需要大的摆幅。同时由于M7和M8的栅极电容构成了Ao的容性负载,所以2个管子不能太大。辅助运放如图3所示。Ao的拓扑结构和Ap类似,但采用PMOS管作为输入对管。

由于辅助运放主要为主运放提供增益上的改善,不需要太快的速度和建立时间,因此它的尾电流一般为主运放电流的1/10~1/4,大大降低了整个电路的功耗和面积。且由于增加了增益提高辅助运放、即使采用最小尺寸也很容易实现100dB以上的增益,因此主运放中各MOS管均采用最小尺寸,这也可以有效地提升非主极点的位置,而辅助运放则不需要使用最小尺寸。

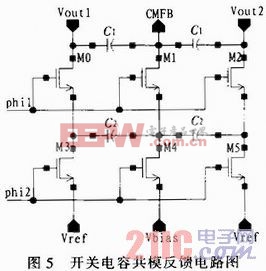

1.4 共模反馈

因为采用全差分结构,放大器的输出共模特性对器件的不匹配非常敏感,由于放大器的输出阻抗较高,很小的电流偏差也会使作为电流源的MOS管进入线性区而不能正常工作,且此情况不能通过差动反馈进行遏制,所以必须在输出端增加共模反馈电路(CMFB)来改善输出特性。

由于本设计的运放要应用于Pipelined ADC中,故主运放采用开关电容(SC)共模反馈,如图5所示。开关电容共模反馈电路工作在两相不交叠时钟下,当phi2为高电平时,C2充电到Vref-Vhias。而当phi1为高电平时,C1与C2相连,C2进行放电,从而决定C1上的电压值。共模反馈电路产生的调节信号CMFB则由C1通过反馈回路产生。使用开关电容共模反馈电路既町以节省功耗,又使取样电路不会限制主运放的输出百幅。本文引用地址://m.amcfsurvey.com/article/186166.htm

但是,开关电容共模反馈电路并不适合两个增益提高辅助运放。因为两个辅运放负载电容较小,若采用开关电容共模反馈,电容会更小,导致电路精度下降。且辅运放不需要大的输出摆幅,故文中对辅运放采用传统的连续时间共模反馈。

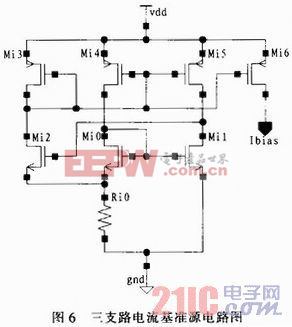

1.5 三支路基准电流源

为提高CMOS集成电路中电流基准的精度和稳定性,一个具有高PSRR的基准电流源是必需的。由于传统的电流基准以及共源共栅电流基准的节点电压正反馈限制了电流基准的性能,三支路基准电流源如图6所示。

此结构由于节点电压成负反馈,拥有更高的PSRR。该基准电流源的输出电流为:![]()

可以看出:其输出电流与系统的电源电压无关而只与调节电阻Rs有关,通过调节合适的Rs的阻值,即可得到精确的基准电流。故本文采用三支路电路基准源的设计,而偏置电路采用低压宽摆幅共源共栅结构。

评论