具有输入过压保护的高端电流检测

图3是 ADA4096-2采用单位增益缓冲器配置时的情况,其中将电源连接至GND(或±15 V)并对正输入扫描,直至输入超过电源达32 V。一般而言,输入电流在正过压条件期间限于1 mA,在负欠压条件期间限于200 µA。例如,在20 V过压条件下, ADA4096-2输入电流限于1 mA,从而提供等效于串联20 kΩ电阻的电流限制。图3还显示,无论是否为放大器供电,电流限制电路均有效。

请注意,图3仅代表异常条件下的输入保护。正确的放大器工作输入电压范围(IVR)见 ADA4096-2数据手册的表2至表4。

AD7920是一款12位、高速、低功耗逐次逼近型ADC,采用2.35 V至5.25 V单电源供电,最高吞吐量可达250 kSPS。该器件内置一个低噪声、宽带宽采样保持放大器,可处理13 MHz以上的输入频率。

转换过程和数据采集过程通过CS和串行时钟SCLK进行控制,从而为器件与微处理器或DSP接口创造了条件。输入信号在CS的下降沿进行采样,而转换同时在此处启动。该器件无流水线延迟。

AD7920采用先进的设计技术,可在下述高吞吐速率的情况下实现极低的功耗,

若要进入关断模式,必须在SCLK的第2个下降沿之后、第10个下降沿之前的任意时间将CS变为高电平,以中断转换过程。一旦CS在SCLK的此窗口内变为高电平,器件即进入关断模式,CS下降沿所启动的转换终止,SDATA返回三态。如果CS在第2个SCLK下降沿之前变为高电平,则器件仍将处于正常模式,不会关断。这可以避免CS线上的毛刺引起意外关断。

若要退出这种工作模式并使 AD7920再次上电,需要执行一次伪转换。在CS的下降沿,器件开始上电,并且只要CS处于低电平便继续上电,直到第10个SCLK的下降沿之后。经过16个SCLK后,器件完全上电,下一次转换将产生有效数据。

如果CS在第10个SCLK下降沿之前变为高电平,则 AD7920再次返回关断模式。这可以避免CS线上的毛刺引起意外上电,或者CS位于低电平时8个SCLK周期意外爆发。虽然器件可以在CS的下降沿开始上电,但只要不超过第10个SCLK下降沿,便会在CS的上升沿再次关断。

有关时序的详情请参见 AD7920数据手册。

测试结果

衡量该电路性能的一个重要指标是最终输出电压测量结果中的噪声量。

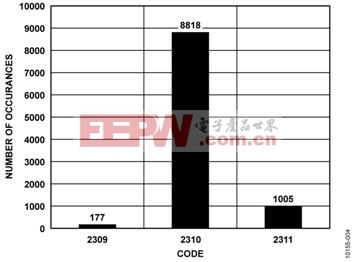

图4显示了10,000个测量样本的直方图。该数据是利用连接到 EVAL-SDP-CB1Z系统演示平台(SDP-B)评估板的CN-0241评估板获得的。设置详情参见本电路笔记的“电路评估与测试”部分。

电源设置为3.0 V,不关闭LDO的输出,在250 kSPS的最大速率下采集10,000个数据样本。图4显示了采集结果。峰峰值噪声约为2 LSB,对应于大约0.3 LSB rms。

图4. 关断前10,000个样本的码字直方图

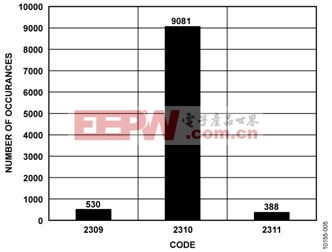

接着在软件中将连接至ADP3336的SD关断引脚置位低电平,从而关闭LDO输出。约1分钟后,再将ADP3336的关断引脚置位高电平,重新开启输出,并采集相同数量的数据样本。图5显示了采集结果。

图5. 关断后10,000个样本的码字直方图

上图显示,输入处于高电平时, ADA4096-2 的输出在关断期间并未闩锁。

常见变化

经验证,该电路能够稳定地工作,并具有良好的精度。该板同时兼容系统演示平台SDP-S控制板EVAL-SDP-CS1Z)。

图1所示电路稍作更改,便可针对最高达+30 V的输入电源电压监控电流。 ADA4096-2的+V引脚并未连接到 ADP3336的+5 V,而是直接连接到受监控的输入电源。在这种配置中, ADA4096-2直接采用输入电源供电。

电路评估与测试

本电路使用EVAL-CN0241-SDPZ电路板和 EVAL-SDP-CB1Z 系统演示平台SDP-B控制器板。这两片板具有120引脚的对接连接器,可以快速完成设置并评估电路性能。 EVAL-CN0241-SDPZ板包含要评估的电路,如本笔记所述。SDP-B控制器板与CN0241评估软件一起使用,可从 EVAL-CN0241-SDPZ电路板获取数据。

设备要求

带USB端口的Windows® XP、Windows Vista®(32位)或Windows® 7(32位)PC

EVAL-CN0241-SDPZ电路评估板

EVAL-SDP-CB1ZSDP-B控制器板

CN0241 SDP评估软件

能够驱动6 V/1 A的直流电源

能够驱动5 V/2.5 A的直流电源

2 Ω/12 W负载电阻

开始使用

将CN0241评估软件光盘放进PC的光盘驱动器,加载评估软件。打开“我的电脑”,找到包含评估软件的驱动器。

功能框图

电路框图参见本电路笔记的图1,电路原理图参见“EVAL-CN0241-SDPZ-SCH-RevA.pdf”文件。此文件位于 CN0241 Design Support Package中。

评论