开关电源EMI滤波器设计

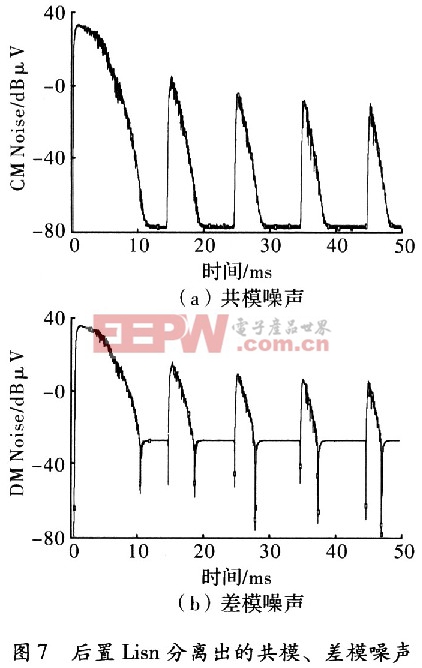

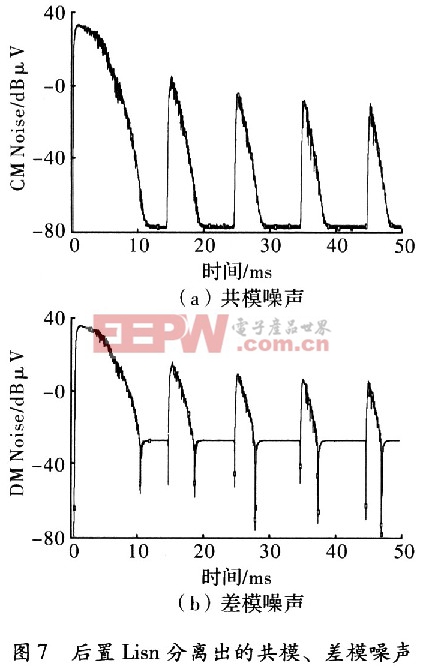

为了验证滤波器对CM、DM噪声的抑制作用,可以在滤波器输出端添加图5所示Lisn,分离出共模、差模噪声,如图7所示。本文引用地址://m.amcfsurvey.com/article/187856.htm

如图7所示,共模噪声最大值为32 dBμV(1 ms),在时域分析7 ms后出现负值。差模噪声电平最大值为3.94 dBμV(1 ms),时域分析3 ms后出现负值,说明在滤波器输出端共模、差模噪声得到了较好的衰减。

2.3EMI滤波器源及负载阻抗特性对插入损耗的影响

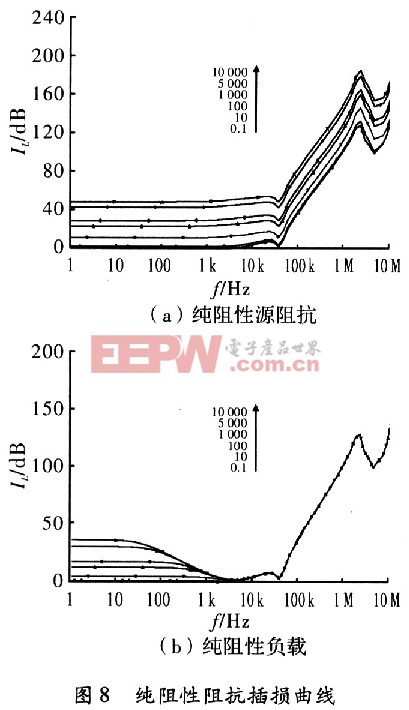

2.3.1 纯阻性阻抗对插损的影响

图8(a)所示,源阻抗ZS为纯阻性,在1 Hz~30 MHz频段插损随着ZS的增大逐渐增大,图8(b)负载阻抗为纯阻性,在低频段插损随着ZL增

大逐渐增大,但在高频段负载变化几乎对插损没有影响。

2.3.2 感性阻抗对插损的影响

图9(a)源阻抗为纯感性(不考虑寄生参数),随着电感值的增加插损在f>1 kHz频段逐渐增大,谐振点插损相应提高。但在f1 kHz,插损几乎不随电感取值的影响。图9(b)源阻抗为感性(考虑寄生参数),插损随电感值的增大而增大,f>1 kHz插损与图9(a)比较下降约30~50 dB,f1 kHz,低频插损与图9(a)比较略高3~5 dB。图9(c)负载为纯感性(不考虑寄生参数),随着电感数值逐步增大,插损几乎没有变化,但在1~10 kHz频段插损随着电感增大而逐步增大。当电感取值>100 mH后,出现谐振点,而且随着电感值的增大,谐振点向工频靠近,谐振点出现极大值。通过选取适当的电感来抑制更接近50/60 Hz的低频干扰,前提是负载必须为纯感性。图9(d)中负载为感性(考虑寄生参数),在低频段插损随着电感增大而逐步增大,但在高频段插损几乎没有变化。

评论