宽带CDMA发射机低相噪本振源的设计

b.分频比的确定

由于本项目的信道宽度为2.5MHz,因此理想的比较频率应为2.5MHz。此时,分频比N为1470/2.5=588,但LMX2347仅能产生992到32767范围内的连续分频比,因此,决定选择比较频率为1.25MHz。做出该选择副作用是由于N值的增加,整体相噪会增加3dB。即使LMX2347的相噪特性下降3dB,其整体特性仍至少优于其他芯片-210-(-220)-3dB=7dB。而且实际仿真表明,当比较频率为1.25MHz时,EVM为1.66%,仍旧满足设计要求。

3.3 VCO的选取与指标设定

相位噪声是VCO设计的关键指标。由公式(5)求得合理的VCO在10kHz上的相噪为-95dBc/Hz。

其中,k为相位噪声谱中带内最低相噪密度,单位是dBc/Hz,p是带内峰值相噪。

为减小VCO输入电容对环路滤波器的影响,规定其输入电容应小于10pF。

图片看不清楚?请点击这里查看原图(大图)。

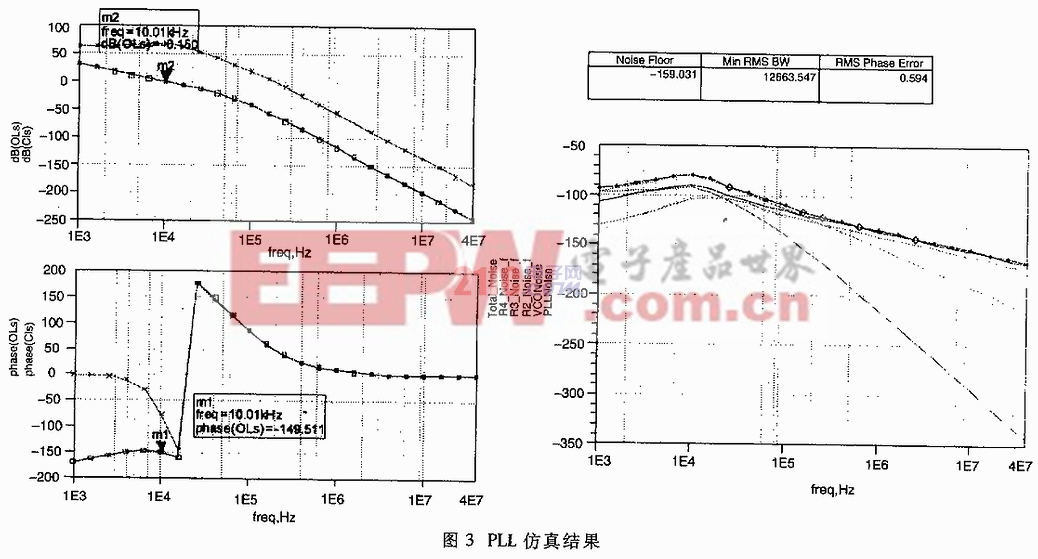

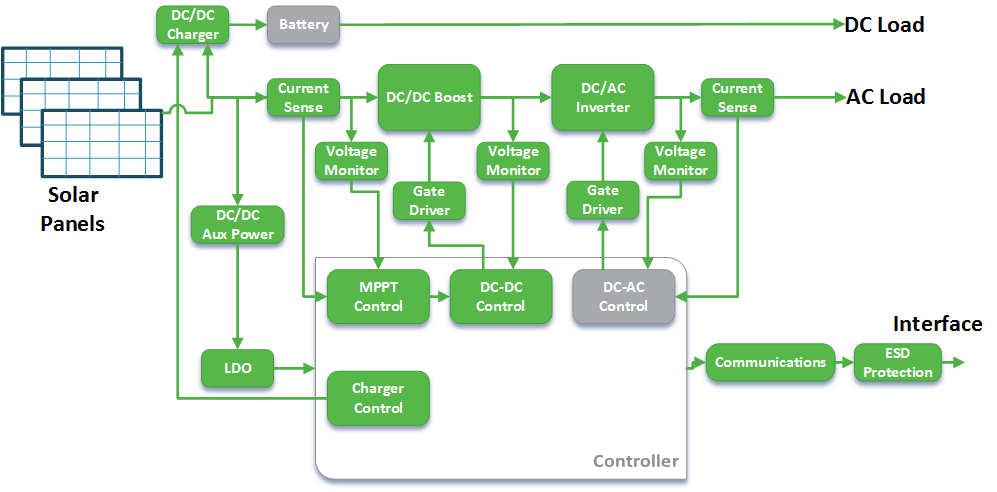

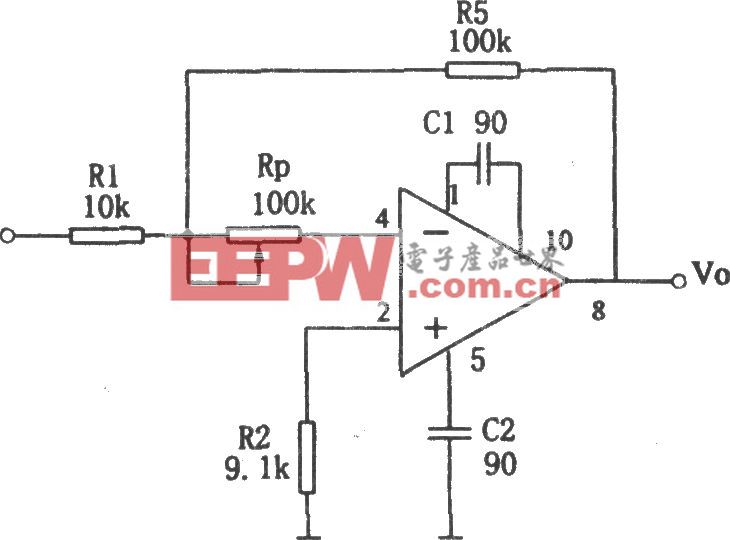

图3 PLL仿真结果

4 电路设计与仿真

为了方便电路的设计与调试,笔者编写了一套ADSPLL仿真程序。该程序可以灵活地选择滤波器阶数,并可在每次参数变化后一性给出与该次变化相对应的相噪、杂散、相位余量等参数,使设计者在器件值变化后可了解PLL的整体特性。

仿真软件以环路滤波器Z参数中的Z21代表环路增益,从而使得环路滤波器拓扑结构可以随便调整。另外,由于ADS软件自身的优点,该仿真软件可以对任何指标进行参数优化,从而得出最优的电路参量。在相位噪声方面,该仿真程序考虑了1Hz鉴相器相噪、VCO相噪以及环路滤波器各电阻所引入的噪声。总噪声为各部分噪声在PLL输出端的叠加,如(6)式。

TotalNoise(f)=10log(10PLLNoise(f)/10+10CCONoise(f)/10+10R2-Nsise(f)/10+10R3_Noise(f)/10+10R4_Noise(f)/10+10TotolSpur(f)/10) (6)

该程序给出了PLL电路的开环增益及相位变化。相位余量对应于增益为0dB时的相位变化。考虑到本振源对ACPR参数的影响,在该仿真程序中加入比较频率上的杂散噪声。

PLL IC的杂散噪声由漏电杂散噪声(Leakage Spur)和脉冲杂散噪声(Pulse Spur)构成,其计算公式分别为:

LeakageSpur=BaseLeakageSpur+20log(LeakageCurrent/kφ)+SpurGain (7)

PulseSpur=BasePulseSpur+SpurGain+40log(Fcomp/1・Hz) (8)

其中,BaskLeakageSpur为常量16dBc,LMX2347的BasePulseSpur为-322dBc,SpurGain为杂散频点上的环路增益,Leakage为电荷泵在三态高阻上的漏电流,Kφ为鉴相增益,Fspur为杂散频点的频率。

为增强对杂散噪声抑制以提高邻道抑制(ACPR)性能,并考虑到1.25MHz的比较频率,本设计采用4阶环路滤波器,在仿真过程中主要以杂散噪声抑制为优化目标,优化仿真结果如图3,其中标“□”的线为闭环增益与相位响应,标“×”的线为开环响应。“○”线为总相位噪声。

(1)相位噪声参数:根据仿真生的相噪密度,求得PLL电路产生的RMS Phase error=0.95°,EVM为1.66%2%,满足指标要求;

(2)定时间:664.5μs;

(3)稳定性:相位余量32°;

(4)2.5MHz上相噪与杂散之和为-157.4,可见该本振源的杂散噪声对2.5MHz上的ACPR影响极小。

评论