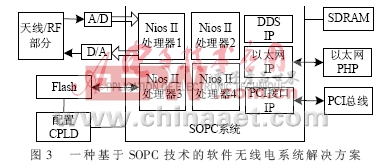

基于SOPC技术的软件无线电系统研究

该系统的功能实现如下:由Nios II处理器1完成原来由ASIC完成的数字上、下变频处理,可通过调用直接数字合成器DDS(Direct Digital Synthesizer)IP模块来实现;Nios II处理器2主要完成调制/解调工作;Nios II处理器4主要完成编码/解码工作;Nios II处理器3用来替代原系统中的GPP完成系统参数的动态配置、人机交互界面、电台管理和控制以及系统中Flash配置内容的在线更新工作。其中,Nios II处理器1、2、4都采用Nios II/f高速型32位内核; Nios II处理器3采用Nios II/s标准内核。此外,利用PCI IP核在FPGA中增加了32 bit的PCI Slave总线接口,省去传统方案中所需的1块专用PCI接口芯片;加入了以太网IP核,配合外部以太网PHY接口芯片为系统扩展了以太网接口,以便支持设备通过网络远程对系统进行配置和管理;增加了SDRAM控制器,为系统外扩了SDRAM存储器,进一步增强了系统的数据处理能力。

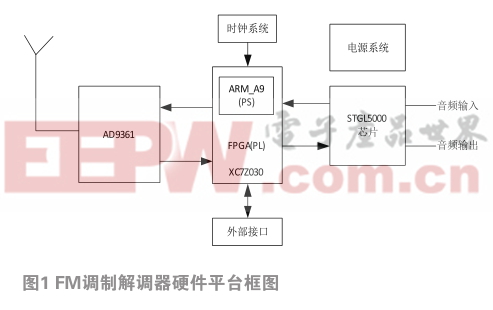

3 系统的软硬件实现

下面就高速数字信号处理部分的硬件选型以及SOPC技术的开发流程、开发工具和编程技术作简要介绍。

3.1 高速ADC和DAC设计

软件无线电要求ADC、DAC尽可能地靠近天线,这需要ADC具有很高的采样率、采样精度和动态范围等特征。本系统的ADC采用BB公司的ADS5520,它具有12位的分辨率,125 MS/s的采样速率;在100 M信号输入情况下,信噪比(SNR)高达69.7 dBFS,无寄生动态范围(SFDR)高达82 dBC;芯片既支持3.3 V的单电压供电,也支持2.3 V的差分输入电压;具有串行编程接口,可对内部寄存器进行编程,使器件工作在不同的状态。

DAC采用BB公司的DAC904芯片,14位的分辨率,165 MS/s的转换速率;可以3.3 V或5 V单电压供电。信号输出端使用截止频率为120 MHz的低通滤波器,以及双端到单端变换电路。

3.2 FPGA的设计

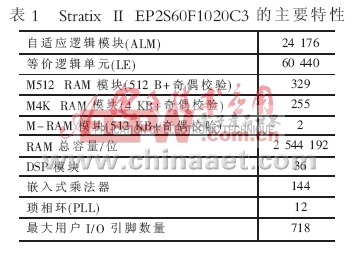

本平台的FPGA器件选用Altera公司的Stratix II FPGA。在Stratix II FPGA中,Altera引入了全新的逻辑单元体系结构――自适应逻辑模块(ALM),以及经过改进的片内TriMatrix存储器和数字信号处理(DSP)模块,进一步提高了性能[5]。根据现有的实验室条件本系统选用ALTERA公司的Stratix II EP2S60F1020C3型号的FPGA,它的主要特性如表1所示。

考虑到在Stratix II系列器件上,Nios II/f内核仅占用1 800个逻辑单元却可以达到超过200 DMIPS的性能,可以计算出前面设计的4个Nios II处理器再加上一些外围接口模块和用户逻辑,总共占用的LE资源不会超过40 000。这款FPGA完全满足系统的需求,剩余的资源可以留为以后系统升级所用。

3.3SOPC的软硬件开发技术

SOPC设计包括以Nios II软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、IDE环境的软件设计、软件调试等。SOPC系统设计的基本软件工具包括:(1)Quartus II,用于完成Nios II系统的分析综合、硬件优化、适配、配置文件编程下载以及硬件系统测试等;(2)SOPC Builder,它是Nios II软核处理器的开发包,用于实现Nios II系统配置、生成以及与Nios II系统相关的监控和软件调试平台的生成;(3)ModelSim,用于对SOPC Builder生成的Nios II的HDL描述语言程序进行系统功能仿真;(4)Matlab/DSP Builder,用于生成Nios II系统的硬件加速器,进而为Nios II系统定制新的指令;(5)Nios II IDE,用于完成基于Nios II系统的软件开发和调试,并可借助其自带的Flash编程器完成对Flash以及EPCS的编程操作。此外,Nios II IDE还包括1个指令集成模拟器、MicroC/OS-II实时操作系统、文件系统以及小型TCP/IP协议栈[6]。

SOPC的开发流程通常包括2个方面:基于Quartus II、SOPC Builder的硬件设计和基于Nios II IDE的软件设计[7]。三者之间的关系如图4所示。

特别值得一提的是,通过Matlab和DSP Builder或直接使用VHDL等硬件描述语言设计,用户可以为Nios嵌入式处理器设计各类加速器,并以指令的形式加入Nios的指令系统,从而成为Nios系统的一个接口设备,与整个片内嵌入式系统融为一体。用户可以根据设计项目按具体要求构建自己的DSP处理器系统,而不必拘于具体的DSP处理器型号。

使用SOPC解决方案带来了整个系统开发平台的统一,和其他解决方案相比,具有体积小、功耗低、成本低的优点。此外,开发环境的集成统一、IP核的使用等缩短了系统的开发周期。基于FPGA的SOPC技术具有很高的灵活性和开放性,这充分体现了软件无线电的优势,是实现软件无线电系统的理想方案。

评论