多通道实时CAN总线模拟器设计

2 系统设计

2.1 系统方案设计

根据通用计算机的总线分类,可采用基于ISA总线对多通道实时CAN总线模拟器进行研制,根据CAN总线通信原理可以提出以下两种设计方案:

(1)ISA总线+CAN通信控制器;

(2)ISA总线+微处理器+CAN通信控制器。这两种设计方案的不同点在于是否采用处理器来加强控制。

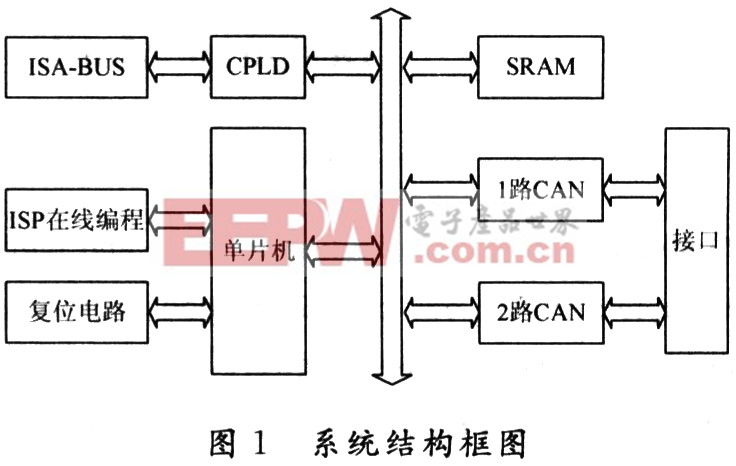

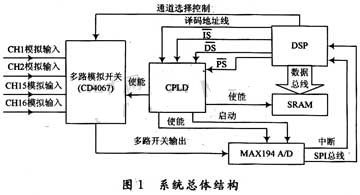

由于CAN总线通信要求实时性高,再加上多通道的设计满足实际的需要,故采用单片机来负责CAN总线的通信功能。在这里主要介绍单片机与CAN控制器之间的设计部分,其系统设计框图如图1所示。本文引用地址://m.amcfsurvey.com/article/188441.htm

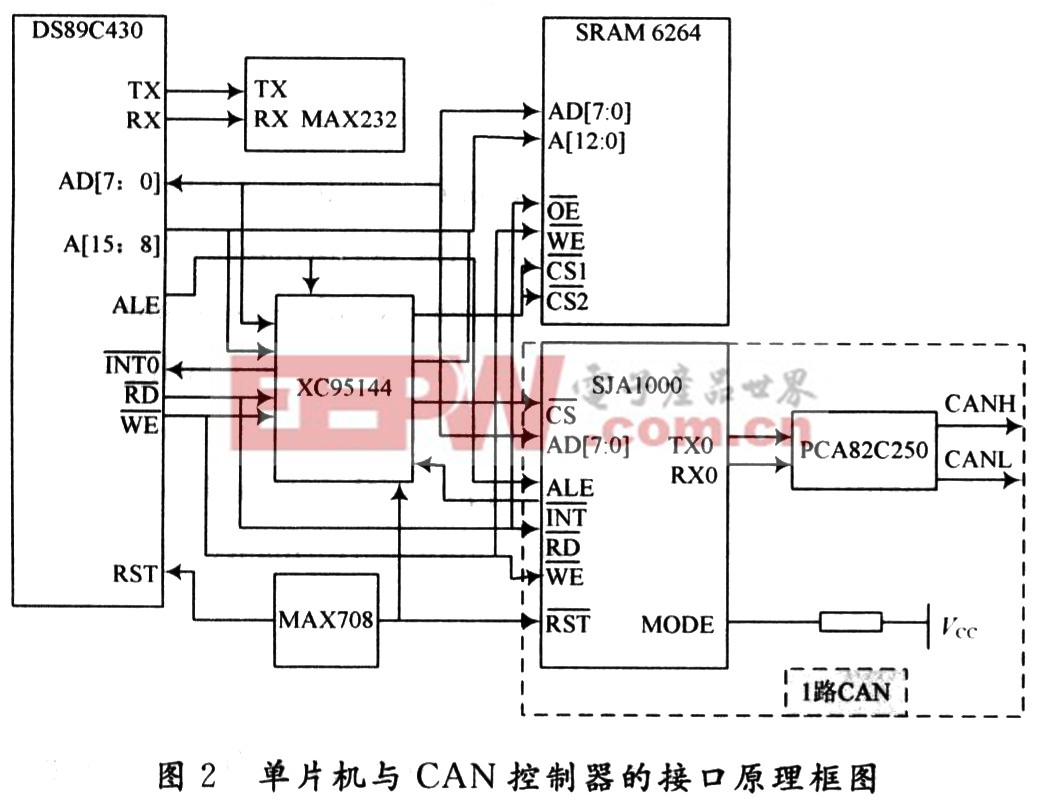

单片机选用DALLAS公司的DS89C430,它是当前8051兼容微控制器中性能最高的。具有重新设计的处理器内核,在相同的晶振频率下,执行指令的速度是最初8051微处理器的12倍。特性:高速8051架构,每个机器周期一个时钟;片内存储器16 KB/32 KB/64 KB闪存,在应用可编程,通过串口实现在系统可编程;与8051引脚和指令集兼容;四路双向、8位I/O端口;三个16位定时器/计数器;256 B暂存RAM等特点。可根据实际应用的需要选择其部分功能。随着可编程逻辑器件的飞速发展,其应用领域不断扩大,可用于译码、解码等方面,使用CPLD可以提高系统集成度,降低噪声,增强系统可靠性。因此,单片机与CAN控制器之间的锁存、译码采用Xilinx公司XC95144CPLD芯片,优化了系统资源,降低了其功耗。

2.2 系统硬件设计

该部分由单片机、CAN控制器、CAN收发器、SRAM存储器组成。单片机主要用于系统计算及信息处理等功能;CAN控制器主要用于系统通信;CAN收发器主要用于增强系统的驱动能力;SRAM主要用于缓存数据。系统的发送过程是:单片机将外围设备传送过来的信息处理后,按CAN规范规定的格式,将其写入CAN控制器的发送缓冲区,并启动发送命令,把数据发送到CAN总线上;接收过程是:CAN控制器从CAN总线上自动接收数据,并经过滤后存入CAN接收缓冲区,且向单片机发出中断请求,此时单片机可从CAN接收缓冲区读取要接收的数据。SJA1000提供的微处理器接口方式为典型INTEL或MOTOROLA地址数据多路复用总线模式。主要信号有地址数据信号AD7~AD0,地址选通信号ALE,片选信号CS,读信号RD,写信号WR,模式选择信号MODE。当MODE=1时,为INTEL模式;当MODE=0时,为MOTOROLA模式。后面描述的总线模式均为INTEL模式。AD7~AD0引脚在ALE有效时,传送的是地址信号,在RD或WR有效时,传输的是数据信号,在这里分别与单片机的PO口相连,RD,WR信号线分别与单片机的读/写信号线相连。具体方案如图2所示。限于篇幅限制,虚线内给出1路CAN的连接图,2路CAN有同样的连接方法。

SRAM和CAN控制器的片选信号。由于单片机可以查询或中断方式访问,在此采用中断方式进行CAN多通道选择访问,以满足不同通信速率下数据处理的需要。SRAM的地址线与数据线是分开的,故采用74LS373锁存器实现锁存功能。可采用XC95144CPLD芯片以及VHDL硬件描述语言以实现锁存、译码等功能。

评论