H.264解码器中一种新颖的去块效应滤波器设计

(1)查找表操作:取得α,β,c1参数。α,β参数均需在查找表操作之前进行基于量化参数与片级偏移参数的计算中使用。当Bs=1,2,3时,为获取c1进行LUT操作,该操作比获取α,β的LUT操作大3倍。

(2)当Bs=4时,需用4或5抽头的滤波器进行滤波,原来的p,q像素值需要进行移位、相加等操作,以得到最后的结果。

3.2 流水线架构

基于上述分析,这里提出了5阶流水线以提高吞吐量,见图3。由于整个任务被分配到不同的阶段实现,降低滤波的平均时间。本文引用地址://m.amcfsurvey.com/article/188527.htm

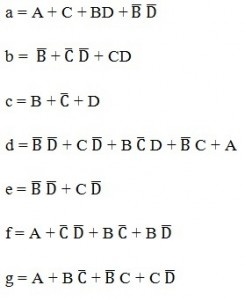

4 阶流水线每个阶段的任务

阶流水线每个阶段的任务为:获取像素与滤波强度;阈值判断;预滤波;二次滤波;回写。操作类型转换与可重新配置路径设计:首先进行操作类型的变换,使用加法与移位操作硬件替换了原来所有的乘法与除法硬件。当Bs=4时,滤波被3,4,5抽头的滤波器执行,尽管应用不同抽头数目的滤波器,仍考虑硬件复用以及输入数据路径重新配置。由于设计中的表达式采用两输入加法,因而可以公用加法的中间结果。此外,通过重新配置在不同滤波抽头系数时的加法器的输入,达到共享资源的目的。同理,当Bs=1,2,3时,通过输入路径的重新配置,同样达到共享加法与减法器,达到共享资源的目的,资源使用前后对比见表1。

5 流水线竞争与混合滤波顺序

5.1 流水线竞争的原因

(1)数据竞争:当目的结果需要用作源操作数时;

(2)结构竞争:由于有限的存储器带宽,大量而频繁的像素访问需要以及存储器的低效率管理而引起;

(3)控制竞争:相邻边界的滤波是相对独立的,当一条边界进入它的流水线阶段时,它不能够停止,直到它的第5阶段新像素值回写存储器操作结束。控制竞争,由于分支语句或延迟等待引起的。

5.2 一种新颖的混合滤波顺序

传统的设计按照H.264/AVC标准使用了基本的顺序滤波,没有考虑到相邻滤波边界的数据重用与数据相互依赖性以及存储器的读与写访问延时,因此这里提出了新颖的滤波方法。新颖的滤波顺序仍然遵守先左后右,先上后下的原则,但是考虑了相邻边界的数据依赖性与重用性,解决了数据冒险与结构冒险问题,避免了流水线的延迟。滤波包括亮度部分与色度部分,共48条边界,滤波顺序按照如图4所示的从小到大的数字进行。

5.3 新颖的存储更新策略

考虑到外部存储器的带宽是32位的,为了配合这里提出的边界滤波顺序,避免由于存储器的带宽限制而引起的结构竞争从而导致流水线出现延迟,这里提出了新颖的存储器更新机制,即给不同的4×4宏块分配不同的时隙进行像素回写。

去块效应模块被分配在整个解码模块的最后一步实现,而其它的重建步骤、像帧内滤波模块、帧间滤波模块均以4×4宏块为基本单位来进行流水线处理,但是由于去块效应滤波模块中不同边界之间的数据依赖关系,因而它是以整个16×16宏块为基本单位进行滤波的。此外,只有整个16×16宏块的像素重建完毕之后.才可以进行该宏块的滤波,因而使用了2个SRAM,一个为像素重建提供像素;另一个为像素滤波提供像素,当一个宏块被处理完毕,两个SRAM交换角色,这样避免在两个SRAM之间传递数据导致的时间与功耗开销。使用仿真工具对整个去块效应顶层模块DF_top进行了仿真,仿真部分结果如图5所示。

6 结 语

使用硬件描述语言完成了设计,并在FPGA平台上得到验证。设计采用流水线技术,混合滤波方法,配合新颖的存储器更新机制等方案,实时滤波频率上限约为200 MHz,吞吐量为滤波每个16×16宏块需要198个时钟周期。使用HJTC,CMOS工艺,使用Syn-opsys Co.的DC工具进行综合,时序分析以及功耗分析,结论是时序满足收敛要求,并且完成单个宏块的滤波消耗的能量大约为2μW,功耗得到了很大的降低。

评论