基于AD9858的雷达信号波形产生器设计

近年来,随着雷达技术的高速发展对雷达信号源的要求也越来越高。宽工作频段、高输出功率、复杂多变的信号调制形式和信号的稳定度已成为衡量雷达信号源性能的重要指标。AD9858是业界首款具有1 Gs/s直接数字合成器(DDS),10位D/A转换器,快速频率跳跃和精细调谐分辨率功能的单片解决方案,AD9858优良的性能使其适用于军事以及航空雷达的信号源设计。

雷达信号波形产生器在有源雷达整体结构中占有重要地位,能在低功率电平上产生雷达信号的基本波形,因而易于得到脉冲压缩和相参系统等所要求的复杂波形。基本波形经过功率放大器后即可送至天线作为雷达输出信号。图1所示为采用功率放大发射机和超外差接收机雷达的简化框图。

|

雷达系统普遍采用的发射信号大敛分为:单频脉冲、线性调频信号及编码调制信号。为了增大探测距离,优化距离分辨率、速度分辨率等技术指标,通常可将这些信号组合来形成波形。采用高速DDS器件AD9858形成的波形信号具有高精度、高扫描率、抗干扰性好、截获率低等特性,而且硬件电路结构简单,有助于设备的小型化和集成化。

3 DDS工作原理

3.1 DDS基本原理

直接数字频率合成(DDS)采用全数字结构,具有精确的频率分辨率、快速的频率转换时间以及可灵活产生多种信号等特点。因此,DDS已逐渐取代模拟方式。DDS合成的原理框图如图2所示。

|

DDS由相位累加器、波形存储器和数模转换器等组成。其原理:向DDS写入频率控制字,经过相位累加器转换成瞬时相位,在外部参考时钟作用下,每个时钟周期相位累加器累加相位步进一次,然后对应到波形存储器中所存储的正弦函数查询表,不同的瞬时相位码输出不同的幅值编码,再将该幅值编码输出给数模转换器(D/A),把数字量转换为模拟量输出给低通滤波器,最后输出所需的信号。

3.2 AD9858简介

AD9858是美国ADI公司的CMOS型DDS集成电路,其内部结构如图3所示。

|

与其他高速DDS器件相比,AD9858内部集成有10位数模转换器,其频率分辨率为32位,最高输出频率可达400 MHz。AD9858的系统结构含有:DDS模块、模拟混频器模块和数字锁相环模块。其中DDS模块可在数字域产生表示正弦曲线的数字值;数字锁相环由数字相频检测器(PHD)和具有高速锁存逻辑电路的电荷泵组成;模拟混频器主要用于通信基站设计。

AD9858有并行和串行两种数据传输方式。数据从用户传输到DDS器件需两步骤:写操作时,不管是采用并行还是串行数据传输方式,首先都要将数据写入I/O缓冲;当数据从I/O缓冲器存入存储寄存器,DDS才开始接收数据。在AD9858中,触发FUD引脚或者改变预编程的Profile都可以使I/O缓冲器中的数据存入DDS的存储寄存器中。

并行模式时,系统激活8个双向数据口(DC~D7)、6个地址输人口(ADDR5~ADDR0)、1个读口(RD)和1个写口(WR)。寄存器的选取由寄存器提供的地址决定。读写功能由RD和WR脉冲触发控制,但这两个功能不能同时作用。读写数据通过。D0~D7引脚传输。

串行模式包括两个阶段。第一阶段由一个8位的指令周期构成,最高位是标志位,可确定读写操作,低6位是串行数据传输目标寄存器地址;第二阶段是将数据写入寄存器。

4 系统软件设计

雷达信号发生器是在VC环境下通过计算机并口控制AD9858,来产生雷达发射机所需的各种信号。AD9858有单频、频率扫描和睡眠三种工作模式。可产生单频点正弦信号、CHIRP信号、BPSK(QPSK)信号。

线性调频工作原理:先指定频率起始点和步进频率,并使频率以一定的速率累加,直到用户所设定的上限频率(最高频率为参考时钟频率的一半,即奈奎斯特频率)。以AD9858采用串行工作方式,产生线性调频信号为例,给出控制流程图如图4所示。初始化是指复位AD9858的初始状态,包括设置S/P SELECT,SLEEP,RESET,CLR,SYNC等位。根据产生信号参数分别配置控制寄存器(CFR)、频率调节字(FTW)、步进频率调节字(DFTW)、步进频率斜率控制字(DFRRW)和相位偏移字(POW)等。

|

寄存器设置完成,系统等待外部激励信号。当检测到一个上升沿后,系统发出update信号,将写入寄存器的数据导入DDS内核,DDS按照新配置开始工作。与此同时,计数器开始计数,并输出线性调频信号,并使相位累加器置1。计数器溢出后,系统发出update信号,由于此时相位累加器清零位有效,相位累加器被清零,同时停止输出线性调频信号。其中,写控制字以及update信号的产生都是通过计算机并口实现的。在VC环境下,为方便对并口实施读写操作,本系统设计直接使用由Yariv Kaplan编写的WinIo库,具有如下特点:WinIo库通过使用内核模式下设备驱动程序和其他一些底层编程技巧绕过Windows安全保护机制,允许32位Windows程序直接操作I/O口。库内含有GetPortVal和Set-PortVal两函数即可实现并口数据读写。

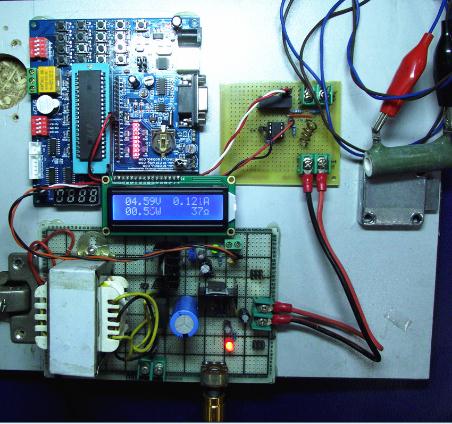

5 系统硬件设计

雷达信号波形产生器基于VC软件编程环境,采用计算机向并行接口读写数据来控制AD9858,再辅以晶体振荡器、滤波器、放大器和混频器等外围电路来实现单频点正弦信号、多普勒信号和线性调频信号等复杂信号。其系统结构图如图5所示。

|

其中DDS器件AD9858的控制信号包括数据线D0~D7、地址线ADDR0~ADDR5、写信号WR、读信号RD、复位信号RESET和频率更新信号FUD。PS0,PS1接地,采用IDC26与外界连接。AD9858只使用其DDS功能部分,锁相环和混频器功能设置为无效。AD9858的参考时钟频率由外部晶体振荡器通过锁相环提供,选用高性能100 MHz恒温晶体振荡器。AD9858的时钟信号倍频模块主要将参考晶振(100 MHz)的频率倍频至DDS所需的参考时钟频率。AD9858所产生的信号由于外围器件影响,必然产生杂散和噪声,因此可通过滤波器滤除噪声,再经过功率放大提高信号电平,从而得到稳定且波形相位幅值均可调的输出信号。该信号即用于雷达的信号源又可用于设备调试的实验信号。

基于VC编程,计算机可产生AD9858所需的6路时序,通过并口送入AD9858。6路信号分别为:RESET主复位信号、FUD更新信号、SDIO数据写入、读出端口、IORESET输入输出同步复位信号、CS片选信号、SCLKAD9858内部串行数据读写时钟。

晶体振荡器的频率在锁相环作用下产生AD9858所需的系统时钟送入AD9858,AD9858产生同步时钟SYNLCLK和所需的信号频率,同步时钟用于协调AD9858与外设同步。

AD9858输出信号经变压达到滤波器正常工作的动态范围,送入滤波器,滤波得到所需信号。

实际电路设计应根据信号幅值、频率和相位等参数适当增加电压或电流放大器以及混频器、变频器等辅助电路。为保证所产生信号频率的纯度和稳定度,减少不必要的噪声干扰,应考虑接地和电磁兼容等措施。

6 结束语

雷达信号发生器基于VC编程,采用计算机并口和AD9858,根据不同需要再配置少量相关辅助电路即可产生多种信号。DDS器件AD9858优良的性能和计算机并口强通用性,使得雷达信号发生器具备实用性强、可军民两用、电路结构简单、信号参数灵活可调、稳定度高等特点。

评论