短波扩频猝发通信系统的DSP+FPGA实现方案

同步序列由48个32位Walsh序列构成,采用了级联编码。第一层编码为沃尔什序列加扰码。对于沃尔什序列来说,同步情况下的自相关和互相关性能很好。但是在非同步的情况下,沃尔什序列的正交性变差,相关函数有较大的旁瓣值,造成信号间的干扰。为减小旁瓣值,改善Walsh码的特性,用扰码乘以沃尔什序列,得到的新码作为前导序列的内码,则相关性能得到改善。第二层是对Walsh序列与48个相位组合的相乘,其中48个相位组合为 /4,3 /4,- /4,-3 /4的排列组合。经Matlab仿真取一组使所得到的相关峰较为理想,如图2所示。

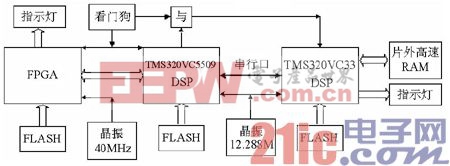

本系统采用TI公司的高性能浮点数字信号处理器TMS320VC33和定点的TMS320VC5509两片DSP芯片作为系统的中央CPU,并采用ALTERA公司的Cyclone系列F

PGA设计出高速数字相关器,用于前端的信号同步与捕获,三个芯片协同工作,并以此为主体架构系统的整个硬件工作平台。

主要芯片介绍

TMS320VC33是TI公司推出的高性能浮点运算DSP芯片。由于其较高的性能价格比,使其应用较为广泛。它的结构允许它以定点的速率完成浮点操作,因此非常适合于做高速高精度的浮点运算,这一优点对于像短波信道快速估值等实时性精确度要求特别高的数字信号处理应用显得尤为重要。TMS320VC5509处理器是TI公司最新推出的高性能低功耗定点数字信号处理器TMS320C55x系列中的一员。TMS320C55x系列是在C54x系列的基础上发展起来的,能与C54x兼容,不仅增加了硬件资源,也优化了资源管理。

TMS320VC5509运行速度快,还可以进行多种并行操作,片内外设资源也比较丰富,与外围设备的连接很方便,所以非常适合用来作控制用。根据上述两种处理器的特点,综合考虑系统的设计要求,我们把TMS320VC5509作为系统的主处理器,而TMS320VC33作为其协处理器。

本文是采用Cyclone系列芯片来实现数字相关器对采样点值进行一次相关,将相关结果送给中央处理器DSP,进行下一步的同步和解扩等处理。ALTERA公司的Cyclone器件具有专用电路,可以实现双数据率(DDR)SDRAM和FCRAM接口。Cyclone器件最多有两个锁相环(PLL),共有六个输出和四种层次化结构,为复杂设计提供了强大的时钟管理电路。

系统硬件模型框图及概述

首先从电台接收过来的基带扩频信号是差分输入的,先经过一个1:1的隔离变压器变为单端输出,再经过运放将其抬高到直流电平以上,低通滤波后送到模数转换器AD7492进行采样处理,采样结果在FPGA中锁存,并在FPGA内部进行希尔伯特变换和相关处理。在一个样点间隔内,进行当前样点值的希尔伯特变换,同时并行地进行前一个样点的相关运算。将相关结果分成四个部分,锁存在对应的四个地址中,由TMS320VC5509分四次依次读取。由TMS320VC5509和TMS320VC33完成信号的捕获和码元的判决。将处理好的数据通过TMS320VC5509送到数模转换器TLV5619中进行数模转换,转换得到的模拟信号经过低通滤波和运放放大以后,再通过同样的一个1:1的隔离变压器变为差分输出送到扩频电台。如图3所示为系统的核心部分。

评论