基于FPGA的数字中频接收和恢复系统设计

4 系统工作原理

FPGA是系统的核心,FPGA从TLK1501中接收数据,经过处理后,将有效数据送到AD9957并行数据输入端口,由AD9957完成信号的恢复。

系统中光纤的传输速率为1.2Gbit·s-1,在TLK1501中经过10b/8b解码后,其有效数据的传输速率为960 Mbit·s-1,经过时钟恢复,数据对齐后,转换为16位并行数据输出,等效并行传输速率为60 MHz,因此,FPGA需要为TLK1501提供60 MHz的配置时钟。

TLK1501中接收到了并行数据,在FPGA中需进一步的处理,分离出帧命令字,提取有效数据,并进行CRC校验,其信号处理流程如图6所示。本文引用地址://m.amcfsurvey.com/article/190001.htm

,系统借助FPGA寄存器资源和并行处理数据时高速流水线优势,根据数学算法上的超前位计算原理,系统实现高速有效的CRC计算,很好地使资源和速度平衡。在CRC校验正确的情况下,进行下一步处理。当前帧输出的前25 Byte为系统的控制字,最后的2 Byte为CRC校验的高8位和低8位,在此单独分离出来,剩余的数据位为有效数据。

在进行数据缓存时,系统采用乒乓操作实现。提取出来的有效数据通过“输入选择”单元将数据流交替分配到两个数据缓冲区,在本系统中,数据缓冲模块采用双口RAM实现。在第一个缓冲周期,将输入的数据暂存到“双口RAM1”,在第2个缓冲周期,通过“输入选择”单元的切换,将输入的数据暂存到“双口RAM2”,同时“双口RAM1”中暂存的第1个周期数据通过“输出选择”单元的选择,由AD9957控制逻辑按照时序要求并行输出;在第3个缓冲周期通过“输入选择”单元的再次切换,将输入的数据暂存到“双口RAM1”,同时“双口RAM2”暂存的第2个周期数据通过“输出选择”单元的切换,由AD9957控制逻辑时序要求并行输出,如此循环。通过“输入选择”单元和“输出选择”单元按时钟节拍、相互配合的切换,将经过缓冲的数据流连续地送到“数据流运算处理模块”进行运算或处理,实现了对数据流进行流水线式的处理,完成数据的无缝缓冲与处理。

5 测试结果

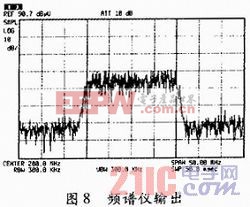

在雷达中频采集后,经过预处理,得到宽带为20 MHz的零中频信号,并通过光线传输到系统中。FPCA通过合理的配置TLK1501和AD99 57,将接收到的数据上变频到200 MHz。图7为SignalTap逻辑分析仪采集到宽带为20 MHz的零中频信号时域波形图,图8为频谱仪观测到的AD9957在正交调制模式下的输出结果,从输出可以看出,信号中心频率为200 MHz,信号的带宽为20 MHz,从而验证了系统设计的正确性。

6 结束语

系统以FPGA为核心,设计了一款高速、高性能的数字中频接收和恢复系统。本设计具有以下特点:采用光纤通信技术,实现了数字信号的实时接收,具有传输误码率低、工作性能稳定、抗干扰性强的优点;采用DDS技术,实现了输出高稳定度的数字正交调制要求。FPGA较大的灵活性为系统的实现提供了保证,硬件结构简单,功能清晰明了。但是,TLK1501依旧没有把光线通信的优势充分体现,EP1AGX20CF48416内部含有光纤收发器,若用FPGA内部的光纤收发模块,则可进一步提高传输速率,改善系统的性能。

评论