CC2530和FPGA的新型无线网络节点设计

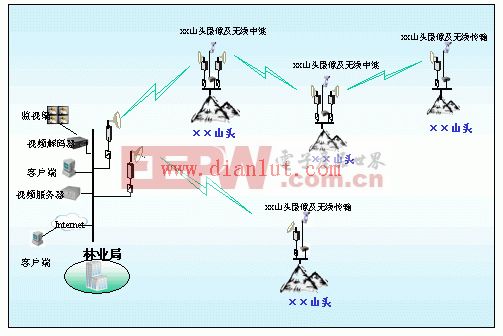

图2的ZigBee网络中,路由器既能收发数据,也能充当路南器,转发数据。实际上,中心协调器本身和路由器没有区别。而在一个网络里,必须把某个路由器作为主节点,并没置整个网络所共用的PAN ID,例如所有路由器的出厂PAN ID都设为PAN ID=0x199B。在组网时,需要把其中一个路由器作为主节点,设置除0x199B的0x0001~0xFF00中的任意的PAN ID。在这个网络里,有唯一的PAN ID,任意想要加入网络的节点,需要设置为相同的PAN ID才可以加入。该网络中的任意两个节点都可以进行通信,即使其他节点都断电了,当然也有可能中心协调器也断电,这两个节点间还是可以进行通信的。

2 节点的构成

2.1FPGA具体配置

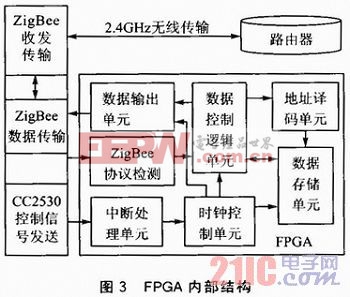

本文采用的FPGA主芯片是Altera公司的EP1C6Q240C8,它有240个引脚、6 030个LE以及26个M4K结构的片上RAM(共计239 616位),而且含有2个高性能PLL以及多达185个用户自定义的I/O口。由于该器件是FPGA与CC2530的协调操作,所以FPGA需要根据CC2530的输入/输出进行配置,而CC2530是既作为MCU,又作为数据传输端的芯片。FPGA内部结构如图3所示。本文引用地址://m.amcfsurvey.com/article/190019.htm

EP1C6Q240C8根据CC2530发送来的控制信号,根据时钟单元对CC2530接收到的数据进行协议的检测。若检测正确,便发送到数据控制逻辑单元,再根据地址译码存入数据存储单元。在需要输出时,也是通过CC2530的信号发送来控制输出。在FPGA中,最重要的便是数据控制逻辑单元,其中包含了控制比较和数据传输的功能。

2.2 CC2530内部设置

MCU与无线传输接收模块使用TI公司的CC2530,具体选用了CC2530F256。它具有256 KB闪存块,VDD为2~3.6V,fc为2 394~2 507MHz。使用C语言对CC2530进行编程,主要是对RF收发器的配置,而对了该器件,需要在控制RF收发器的同时,对FPGA进行控制,部分程序如下:

评论