基于FPGA的数字积分法插补控制器设计与实现

(2)位置计数器

位置计数器有3个寄存器,分别对应于三个轴。其初始值为需要插补的脉冲数目。当积分器每输出一个脉冲,计数器便做减“1”。当位置计数器为零时,则表示到达终点坐标位置,插补结束。

(3)插补积分器

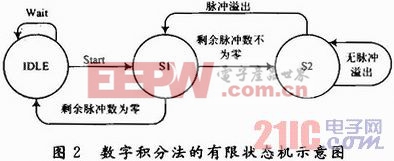

插补积分器是直线插补的核心模块,由余数寄存器和被积函数寄存器构成。被积函数寄存器中存放由数据缓存器提供的终点坐标值,每当脉冲源发出1个插补迭代脉冲时,被积函数寄存器与余数寄存器的值累加1次,并将累加结果存放余数寄存器中,当累加结果超出余数寄存器容量(216)时,溢出1个脉冲。经过N=216次累加后,每个坐标轴的溢出脉冲总数就等于该坐标的被积函数值。在余数寄存器的容量一定的情况下,其输出脉冲频率与终点坐标值的大小成正比。控制器采用三轴联动,则同时有3个积分器同时进行插补运算。在该插补控制器的设计中,采用有限状态机的原理完成直线插补的实现,如图2所示,共有3个状态存在:本文引用地址://m.amcfsurvey.com/article/190545.htm

(1)状态IDLE:空闲状态,等待插补信号;

(2)状态S1:剩余插补脉冲数寄存;

(3)状态S2:积分累加状态。

其工作过程为:当没有启动信号时,系统继续保持在空闲状态IDLE;当有启动信号start时,系统则从数据缓存器中读入初始数据,将插补脉冲数寄存在状态S1中,若插补脉冲数不为零则转至积分累加状态S2中,在此状态中将被积函数寄存器的值与余数寄存器的值进行累加,结果送余数寄存器,若有脉冲溢出,则转入状态S1,此时输出插补脉冲,且状态S1中剩余脉冲数减“1”;若无脉冲溢出,则状态S2继续进行积分累加。最终,状态S1中的剩余脉冲为零时,返回空闲状态,插补结束。

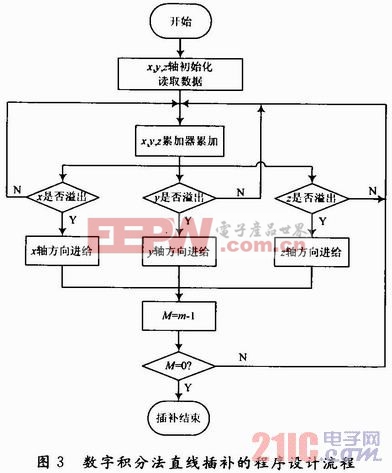

数字积分法直线插补运用硬件描述语言VerilogHDL进行程序编写的流程图如图3所示。

fpga相关文章:fpga是什么

伺服电机相关文章:伺服电机工作原理

评论