ALF简介及IC设计流程

本文引用地址: //m.amcfsurvey.com/article/190690.htm

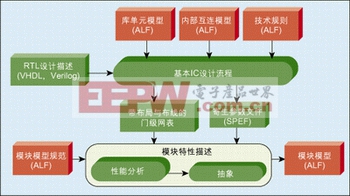

单元布放和内部互连布线过程简称为布局,电源或时钟网络结构之类特殊布局没有在图1中明确表示。ALF单元模型含有抽象物理信息,像单元大小和形状、单元引脚和路由障碍位置、大小和形状等等,这些都与布局有关。

同样,与单元内布线图有关的抽象信息也能在ALF中表示,包括特定层布线区域、边界和连接特性,这些信息与制造能力有关,像天线规则和金属密度检查之类。除了单元模型,布线规则也在ALF中表示,这部分包括布线段宽度和长度的限制、布线段之间的距离以及通孔之间的距离等。

已实现的IC不仅要按功能和布局进行校正,还必须满足电气性能条件制约,主要是时序方面,其它电气性能如功耗、信号完整性和可靠性也变得越来越重要,信号完整性指信号波形的干净程度、对串扰噪声的抵抗性和电压降。

可靠性是指在电迁移应力、热电效应和热不稳定性存在情况下的长期运行稳定性。ALF单元模型支持用于时序、功率、信号完整性和可靠性的数据描述,如可靠性数据可描述为对电压、电流或工作频率的限制条件。

ALF的一个特殊之处是这些数据在激励中的表达方式,它通过矢量表达式进行表述,数据可用这种特性与特定环境的运行条件联系起来,以完成更为精确的性能分析。

IC实现过程每一步都要进行性能分析,RTL综合、单元布放和互连布线应用已经包含了静态时序分析(STA)和其它性能分析功能。同样,在每步完成之后,还可进行独立的性能分析,以便更精确地测量得到的性能。

电气性能不仅取决于单元间的相互作用,还与连线所引起的寄生现象有关。网表生成以后,寄生参数可以用线负载模型(WLM)进行统计预估。布局后通过预先估算布放单元引脚间特定的布线长度能精确预计到寄生参数,布线完成后,实际寄生参数利用标准寄生参数交换格式(SPEF)在文件中进行提取和表达。

ALF互连模型能够描述统计的WLM,它是一个根据估计的布线或互连分析模型进行寄生参数评估的规则。互连分析模型可以指定寄生现象所需间隔,以及根据寄生参数示例和驱动器单元电气模型来计算时序、噪声、电压和电流。特定驱动器单元电气模型所用数据在ALF中表现为单元特性数据的一部分。

IC分层实现与原型生成

以单元作为构建模块的IC实现流程受到单元和网络等目标数目的制约,可由设计人员和应用流程进行处理。对于超过目标限制但还可以处理的IC,可以使用下面方法,这些方法也可组合使用。

* 自底向上设计:首先由单元创建较大的构建模块,然后使用这些模块来实现IC。

* 自顶向下设计:首先将设计分成子设计,实现子设计作为模块,然后将这些模块组装起来。

* 原型制作:首先为整个设计做一个简化所谓的虚拟实现,然后将虚拟实现分割为不同的模块,使用虚拟实现的结果作为每个模块实际实现的限制条件,最后再把各模块组装起来。

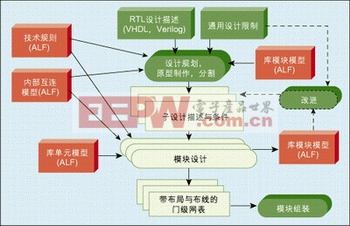

所有这些方法的共同点是创建模块,以减少应用面对的对象数量,模块创建流程见图2。

模块可用基本IC实现流程来创建(见图2),可以再使用的模块一般称为IP。对“硬”模块来说,实现流程主要的输出是带布局布线的门级网表,保存下来后最终转换为物理布线图,而“软”模块只有设计主要输出即RTL设计表述被保存下来。

设计流程输出只用于模块描述,即创建用于模块的抽象模型,模块描述包括了在特性描述和接下来的抽象中反复进行的性能分析。抽象含有减少物理实现数据以及性能分析数据和特定模型的关系方面的内容,模型规范和模型本身两者都能用ALF进行表述。

流程的变量包括IC部分实现,如只做RTL综合和布放而没有布线,这特别适用于不保留实现数据的软模块。不保留模块实现数据的概念是通过之后在其它模块上下文中完成,而不是在前端单独实现,这样可获得更好的整体性能效果。

根据模块是用作硬模块还是软模块,ALF模型能表述不同等级的抽象。用作硬模块的ALF模型具有和单元ALF模型相同的特性,此外,网表和表述实现流程输出的寄生参数可部分保留在ALF模型中,特别是在模块边界处。这样就能在一个IC实现的上下文中对相邻模块之间的电气相互作用进行精确分析。另一方面,用于软模块的ALF模型可以表述一个统计范围,或者描述数据的上下边界,而不是“硬”的特性数据,这是因为实际模块实现具有一定程度可变性,此外统计得出的WLM也能装在模块模型中。

ALF支持用参数表示模块特定建模特性,即可用各种物理形状和大小以及可变位宽与特性实现的模块,ALF里的组、模板、静态和动态模板等概念都能这样用。

评论