NiosⅡ系统Avalon总线PWM设计

2.2软件设计

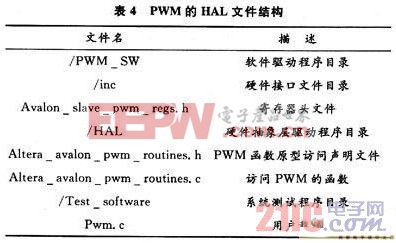

如果要使Nios软核能够访问自定义的设备,就必须根据先前的硬件设计按照硬件提取层的文件结构编写设备驱动程序。以PWM为例说明HAL的文件结构,如表4所示。

2.3 将PWM设计封装为SoPC Builder元件

当硬件文件和软件文件都已建立好后,便可以通过SoPC Builder中带有的设备编辑器将自定义设备封装到开发环境内部,在构建NiosⅡ系统时可以对其直接调用。在SoPC Builder中单击Creat New Component,创建新元件向导添加HDL文件、设置信号和接口添加软件,最终生成包含描述文件、用户存放硬件描述文件的文件夹以及用来包含HAL软件文件的HAL文件夹。

构建好的内核文件在QuartusⅡ中编译,生成pof配置文件下载到E2PROM芯片中,接下来就可以使用Nios IDE开发环境编辑用户程序,以及通过JTAGBlaster或者USB Blaster在目标板上对应用程序进行调试。

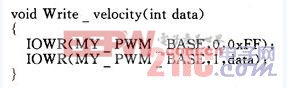

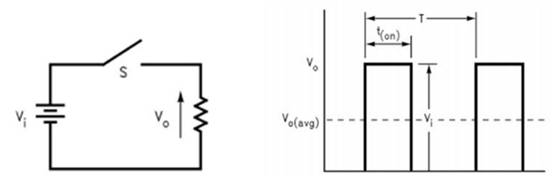

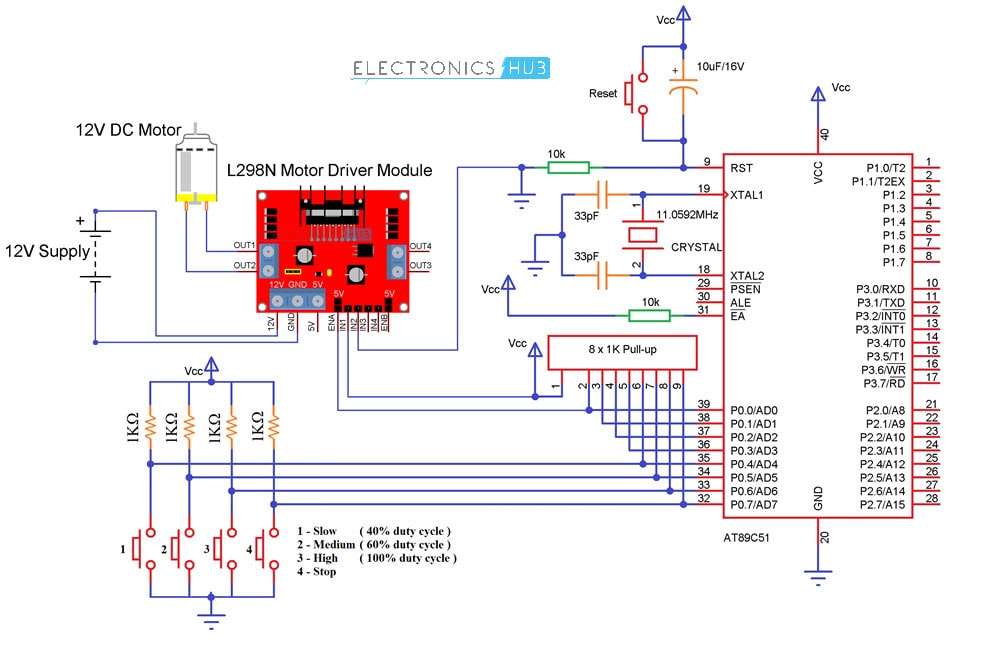

智能小车监控系统设计应用周立功公司SmartSoPC核心板,FPGA为Altera公司的EPlC12,NiosⅡ处理器作为嵌入式CPU,机器人车电机共有两个,左轮电机和右轮电机。该部分包括电机驱动电路和电机控制电路,即左电机的驱动与控制以及右电机的驱动与控制。驱动电路采用CTMicroelectronics公司的大功率直流电机驱动芯片L289,调速控制采用PWM来控制汽车的前进速度,由FPGA写入控制字,可得到不同占空比的PWM驱动信号,此PWM信号送人电机驱动芯片的控制端来调节速度。调用电机驱动程序,改变PWM占空比,输出PWM波,实现电机的速度控制。用PWM信号控制直流电动机速度,频率较低时,电动机不会稳定运转,频率较高时,PWM信号的驱动效率降低。经过多次实际电路的测试,调试结果显示当频率在500~1 000 Hz时,效果较好。部分C语言控制代码如下:

4结 语

NiosⅡ嵌入式处理器是用户可配制的通用RISC嵌入式处理器,是一个非常灵活和强大的处理器。基于此种技术的嵌入式系统设计可以方便地将一般设备和自定义设备模块集成到系统中,丰富了接口资源,从而能使用户快速地开发一个自定制片上系统,提高了效率,缩短了开发周期。本文通过自定制PWM外围设备的方法,并通过硬件测试证明了方案的可行性和正确性,希望能够为采用Nios Ⅱ处理器的开发人员提供一些方法和建议。

pwm相关文章:pwm原理

评论