扩频通信芯片STEL-2000A的FPGA实现

2.4 差分解调模块

当检测到定位脉冲时(即检测到相关峰最大幅值),将此时Isum和Qsum的值送入寄存器以供差分解调使用。对于DQPSK的解调,关键是判断第k位和第k-1位符号之间的相位差△ψ,STEL-2000A中引入点积Dot和叉积Cross来判断△ω。

信号经匹配滤波器后,基带信号可为:I(k)=Acosψ(k),Q(k)=Asinψ(k)。ψ(k)为第k个符号的载波相位。

由于本系统采用DQPSK调制方式,所以△ψ的取值有0,π/2,π和3π/2四种,sin(△ψ)和cos(△ψ)的取值有0,+1,-1三种,在进行最佳判决接收时相对较难实现。本系统引入了π/4的固定相移。给出简单的推导如下:

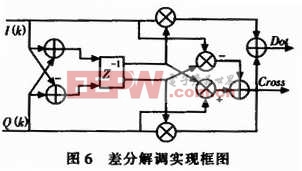

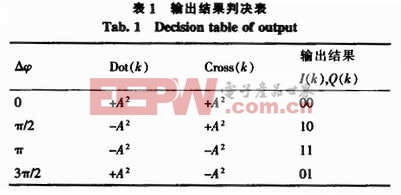

从式(9)、式(10)可以发现只需要在延时之前对两路信号进行简单的算术组合即可得到π/4的固定相移,差分解调器实现框图如图6所示。输出的Dot(k)和Cross(k)值查表1,即可得到最后的差分解调结果。本文引用地址://m.amcfsurvey.com/article/191382.htm

3 测试结果

测试系统为FPGA产生输入信号“01011001”的周期循环序列,输入信号经过发射模块后的数字信号输出直接进入接收模块,输入信号产生模块、发射模块和接收模块都在同一块FPGA芯片内。系统的参数设置为:主时钟为100 MHz,数据最大速率为31.25 Kb/s,工作时钟为31.25 kHz,PN码长为64位,速率为1 Mchip/s,NCO的工作时钟为100 MHz,输出的数字正弦和余弦信号频率为2 MHz。

通过在线分析仪ChipScope Pro,可以看到经QPSK调制后待输出的信号(图7,8),其中图7的I和Q是串并转换后的信号,此时的输入信号为“10110010”,I_chafen和Q_chafen是差分编码后的信号,I_PN和Q_PN信号是经过扩频后的信号,tx_out是最后的已调信号。将已调信号绘制成曲线如图8所示。

在接收部分,利用ChipScope Pro可以观察到下变频器的输出信号I_conv和Q_conv,匹配滤波器的输出信号,Isum、和Qsum定位脉冲sym-bol(图9),I_de和Q_de为差分解调后的信号,图中显示此时的解调结果为“00101011”,相对于输入信号而言只是有一段时延,从而验证该系统实现了STEL-2000A的核心功能。

评论