脉冲压缩原理及FPGA实现

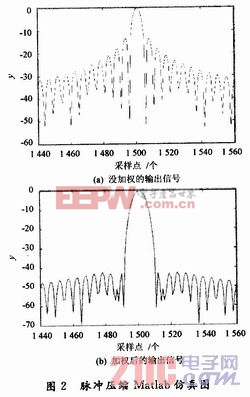

下面,给出仿真信号模型,并在Matlab下进行仿真,以分析加权前后的影响。仿真模型:脉冲宽度为150μs,调频带宽为2 MHz,采样周期为0.1μs,加权方式为海明加权。图2给出了采用加权函数前和采用海明加权函数后的脉冲压缩波形图。

通过海明加权,主副瓣比大大改善,即副瓣得到了显著的抑制。虽然海明加权后带来了一定的信噪比损失,但匹配滤波器的性能得到了大大的提高。

2 分布式算法原理及4阶FIR滤波器的设计

2.1 分布式算法原理

分布式算法(DA)是一种以实现乘累加运算为目的的运算方法,它与传统乘加运算的不同在于执行部分积运算的先后顺序不同。传统算法是在完成乘加功能时,等到所有乘积产生之后,再进行相加来完成乘加运算的。而分布式算法则是通过将各输入数据的每一对应位产生的部分积预先进行相加,形成相应部分积,然后对各部分积进行累加,形成最终结果的。与乘累加算法相比,分布式算法可极大地减少硬件电路规模,降低设计的复杂度,极大地提高可靠性和可操作性。分布式算法由串行、并行和串并结合而构成的分布式算法。串行分布式算法是逐位的执行,每个时钟周期只能执行1位,速度比较慢;并行分布式算法是1个时钟周期完成1个字的运算,速度比较快;串并结合的分布式算法

1次可以执行多位,但是需要多个时钟周期才能完成1个字的运算,控制起来比较复杂。

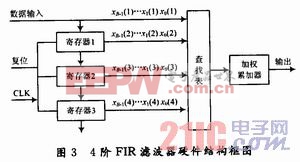

根据分布式算法的原理得出采用FPGA实现分布式算法的硬件结构,如图3所示。

图3中寄存器完成数据寄存,查找表完成数据查找运算,加权累加器完成查表之后的加法。为了保证信号的完整性,即减少输出毛刺,在数据输出前用寄存器寄存一个时钟周期然后输出。

2.2 4阶FIR滤波器的设计

本文的脉冲压缩是通过并行分布式算法来实现的。从图3可以得出,4阶的FIR滤波器主要由移位寄存器、查找表和累加器组成。4为模块的滤波器阶数,那么查找表中应有24个存储单元,如果滤波器阶数过多,查找表规模随阶数的增加成指数递增,因此阶数较大时要分割查找表,分割查找表可以节省存储资源,有利于成本和资源的节约。

要使4阶FIR滤波器完成数据的输入、串/并转换、查表和加权累加,因为是有符号数的运算,所以要考虑累加最高位运算符号。FIR滤波器是线性滤波器,低阶滤波器的输出集合相加,形成一个高阶FIR滤波器的输出。因此,在设计低阶FIR时,必须有2个输出,一个用于FIR运算的输出,另一个输出数据用于下一个FIR滤波器的运算。为了保证信号的完整性,在程序设计时,对输入/输出数据进行了寄存处理。

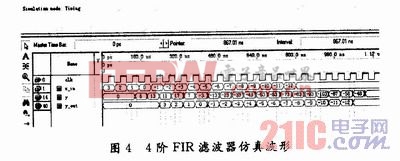

下面给出一个4阶的FIR滤波器设计实例。输入数据为12位有符号数,匹配滤波系数为12位有符号数,4阶FIR的仿真波形如图4所示。仿真结果与Matlab仿真结果完全一致,说明设计是完全正确的。

评论