实时视频数据采集的FPGA实现

2 视频信号采集和显示部分的实现

SAA7113H输出PAL制式的ITU656标准YUV(4:2:2)格式数据[2],其中Y表示亮度信号,而UV表示色差信号,并且输出像素时钟为27 MHz。信号扫描方式为隔行扫描,帧率为25帧/秒,每帧图像分为奇偶两场,每帧像素为864×625,其中有效数据为720×576。SAA7113H 输出的一行视频数据格式如图3所示,每行有1 728 B,其中有效数据1 440 B,对应720个有效像素,可以看成每一个像素由2个连续的字节表示,每个像素有自己的亮度数据Y,每两个相邻像素共用一组色差数据U和V。

由于系统要求在VGA显示器上采用逐场逐行方式显示RGB格式的数据,并且要求所采集图像的大小为640×480,因此,必须对SAA7113H所采集到的原始数字视频信号进行格式转换和存储方式的处理。

2.1 IIC配置单元

视频解码芯片SAA7113H接收CCD摄像头输出的模拟视频信号,将其转换成标准的VPO数字信号。SAA7113H上电后,必须由核心控制芯片FPGA通过IIC总线对其内部的寄存器进行初始化设置,然后才能正常工作。IIC配置单元的任务就是按照IIC总线的数据传输规范对 SAA7113H内部的寄存器进行初始化设置,其时钟信号由SAA7113H提供的27 MHz的像素时钟经过时钟控制单元分频得到,数据速率在100 kb/s~400 kb/s。

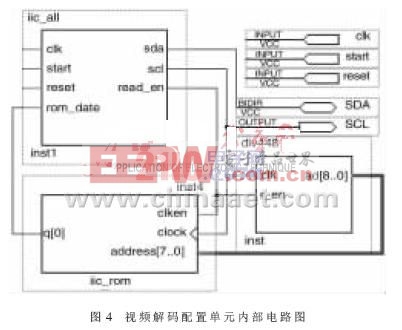

IIC配置单元的内部结构如图4所示,由IIC控制单元iic_all、配置数据存储器iic_rom和读地址发生器div448构成。IIC控制单元iic_all是核心控制单元,采用状态机设计,在start信号有效后使SCL高电平时拉低SDA数据线,同时控制地址发生器div448产生读地址信号送入配置数据存储器iic_rom; iic_rom采用可设置参数模块LPM_ROM,定制为数据宽度为1的只读ROM,每个存储单元按位预存SAA7113H内部寄存器的控制字;在时钟使能端clken有效时按位串行写入SDA数据线。IIC控制单元在start信号有效后的第8个时钟上升沿获取到SAA7113H的低电平应答信号后继续发送数据给SAA7113H,否则将重新回到起始状态等待。

SAA7113H完成初始化配置后,输出数字视频信号VPO[7..0]和相应的同步信号:行有效信号RTS0、奇偶场标识信号RTS1等。其中RTS0高电平表示有效数据行,低电平表示消隐行;RTS1为奇偶场标识信号,高电平表示奇场,低电平表示偶场。

2.2数据采集及控制单元

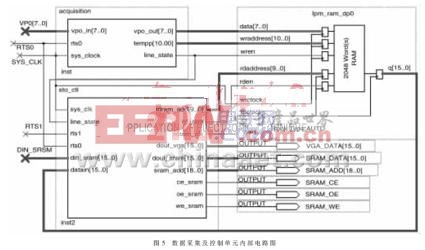

数据采集及控制单元主要由3个模块组成:采集模块acquisition、双口RAM器件lpm_ram_dp0和帧存控制模块 sto_ctl,其内部电路图如图5所示。此单元的任务就是由采集模块截取SAA7113H输出的一行数据中的640个有效像素(共1 280 B)写入双口RAM器件进行缓存,帧存控制模块将数据从双口RAM中顺序读出后送入外扩SRAM中逐行存储,同时控制2片SRAM交替读写,读出的数据送入VGA接口单元进行VGA格式转换和图像显示。

2.2.1 采集模块acqusition

采集模块接收SAA7113H的RTS0、像素时钟信号SYS_CLK和视频数据VPO[7..0],输出为一行数据中的有效数据vpo_out[7..0]、有效像素的计数值tempp[10..0]和表示行状态有效的信号line_state。

评论