基于FPGA的高速同步HDLC通信控制器设计

而多项式乘除法运算过程与普通代数多项式的乘除法相同。多项式的加减法运算以2为模,加减时不进位或错位,和逻辑异或运算一致,即加法和减法等价。则对上述例举的数据的CRC计算过程如图6所示。本文引用地址://m.amcfsurvey.com/article/191467.htm

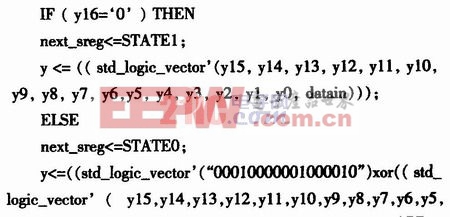

模拟上述计算CRC校验值的方法,不难想到可用状态机实现,设置一个17位的矢量,检验最高位是否为零。如果为零,则跳转到状态1,即所有位左移,最低位补1位数据;如果不为零,则跳转到状态0,最低位补1位数据,与“00010000001000010”异或,(以CRC-CCITT为例,由于y16与‘1’异或必为‘0’,datain与‘0’异或还为datain),这种思路的VHDL代码如下:

图7为该VHDL代码的仿真波形,可看到该方法模拟对2取模整除的一步步计算。

该方法思想简单,是对2取模整除方法的模拟,直观,易于理解,由于是串行输入,不受需要CRC计算的数据位数限制。由于HDLC通信协议的最大优点是对要传输的信息文电比特结构无任何限制,也就是说,信息文电可以是任意的比特串,不会影响链路的监控操作。因此,这里给出的CRC串行算法符合HDLC传输文电比特结构任意的特点。

3 程序加载验证

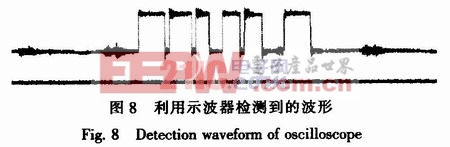

经过逻辑综合和时序仿真后,利用ISE 9.1i集成开发软件将程序烧入FPGA,利用示波器观测FPGA按HDLC通信协议标准发出的信号。如要发送的“有效信号”(不含帧头帧尾,未进行CRC校验及‘O’比特插入之前的原始数据)为“llll llll”,则经过FPGA处理后应发出的数据为“0111 1110 1111 1011 1000 1111 0111 1000 0011 1111 0”,利用示波器检测到的信号波形如图8所示。

由图8可知,对数据进行CRC校验,‘0’比特插入及加帧头帧尾操作,发送数据正确,符合HDLC通信协议标准。

4 结束语

由于HDLC通信协议具有透明传输、可靠性高等优点,在数据链路层应用广泛,而FPGA更具有灵活、高性能、低成本、平台化、可定制等优点,具有系统级能的复杂可编程逻辑器件和现场可编程门阵列实现可编程片上系统也成为今后的发展方向。本文提出的基于FPGA实现HDL-C/SDLC协议方法采用ISE 9.1i编译、综合、仿真、布线、烧写,ISE软件支持器件多,功能强大,操作更方便,因此,该实现方法具有很强的实用性,另外,程序加载入FPGA后发送数据正确,说明该实现方法实用、有效。

评论