基于FPGA的数字幅频均衡功率放大器的解决方案

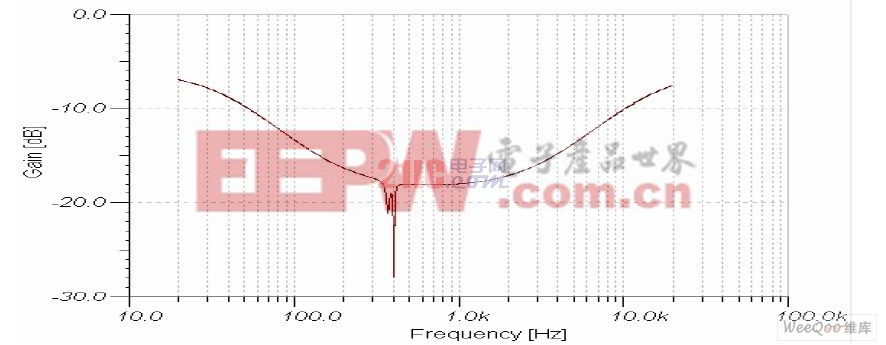

采用Tina 仿真软件中的Signal Analyzer 测得带阻网络输出信号的幅频特性如图2 所示。

图2 带阻网络输出信号的幅频特性

2.3数字信号均衡处理模块电路设计

均衡技术的实质是在某种优化规则下完成随机信号的最优滤波。因此信号的幅频均衡问题即转变为滤波器的设计问题。在大多数使用均衡器的通信系统中,信道特性是未知的;并且在许多情况下,信道响应是时变的,在这种情况下,应将均衡器设计成对信道响应是可调的;对时变信道,应设计成对信道响应的时变是自适应的。所以自适应均衡器在通信系统中得到普遍应用。但本赛题中,因为其采用带阻网络模拟实际的信道,但带阻网络中所有器件参数均为固定值,不存在时变问题,故设计的滤波器系数无需自适应。

均衡模块采用Altera 公司的CycloneII 系列FPGA作为信号滤波处理的核心; A/D 转换模块采用TI 的高速8 位A/D 转换器TLC5540,它的最高转换速率可达每秒40 兆字节;D/A 模块采用10 位高速转换芯片THS5651。

为实现对如图2 所示的衰减进行补偿,均衡模块采用了截止频率均为400HZ 的低通滤波器和高通滤波器的叠加。滤波器组原理图如图3 所示。

2.4 功率放大电路设计

根据题目要求,末级功率放大电路采用分立的大功率MOS 管实现,与分立的OCL 低功放相比,MOS 管功放具有激励功率小,输出功率大,输出漏极电流具有负温度系数,安全可靠,且有工作频率高,偏置简单等优点。电路如图3所示,以运放的输出作为OCL 的输入,达到抑制零点漂移的效果。此方案中用三极管来驱动MOS 管,集基极间的电容C4、C5 为高频防振电容。(注:图中数据为参考数值)

图3 MOS 管功率放大器

评论