基于FPGA的数字幅频均衡功率放大器的解决方案

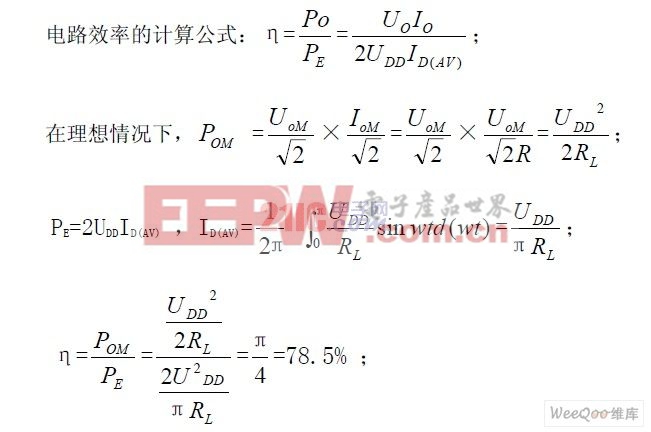

实际功率低于这个值,通过测量来计算出电路的效率。

3 软件设计

Altera 提供了基于Matlab、DSP Builder 的数字滤波器设计方法。使用DSP Builder可以方便地在图形化环境中设计FIR 滤波器,而且滤波器系数可以通过Matlab 的滤波器设计工具FDATool 计算完成。本文中采用直接I 型来实现该FIR 滤波器。首先设计一个系数可变的4 阶FIR 滤波器节。然后再通过不断的调用FIR 滤波器节,级联起来,从而完成高阶滤波器设计。

4 实验结果与结论

图4 singaltap 测试结果

图 4 为采用嵌入式逻辑分析仪SingalTap 得到的测试结果。其中,XIN 为由A/D 采样得到的输入信号,YOUT 为经过均衡程序处理过的输出信号。从输出YOUT 可明显观测到程序对输入信号作出了补偿,去除了噪声,稳定了波形,起到了均衡信号的作用。本设计充分利用FPGA在数字信号处理上的优势,在数字幅度均衡模块中以FPGA为平台,实现数字信号幅度均衡的高速处理。同时本设计中前级放大电路不仅可以满足赛题中的各项指标,还可以实现增益的可选择性,可以在其他小信号放大的场合中运用。

评论