一种基于FPGA的正弦波信号发生器的设计

1.5 低通滤波电路

低通滤波器用于滤除阶梯信号中的谐波分量。本文采用2阶低通滤波电路,阶梯信号通过低通滤波,使得输出信号频谱纯度较好,失真较小。本文引用地址://m.amcfsurvey.com/article/191487.htm

2 系统关键技术

DDS(Direct Digital Synthesis)是一种应用直接数字合成技术来产生信号波形的方法。DDS技术建立在采样定理的基础上,它首先对需要的信号波形进行采样、量化,然后存入存储器作为待产生信号的数据查询表。在输出信号波形时,从数据表依次读出数据,产生数字信号。

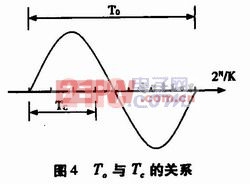

输入时钟频率和输出波形信号的频率关系如图4所示。在图4中To表示输出波形的周期,Tc为采样周期,2N为ROM查询表寻址范围,K为频率控制字。由图可知To=Tc*2N/K,转换为频率可表示为fo=fc*K/2N,fc为时钟信号clk的频率。

在本设计中N=8,因此信号的输出频率fo=fc*K/256。

3 软件设计

软件设计主要是在FPGA中通过Verilog硬件语言进行相位累加器和ROM查询表的编程实现,这两部分采用Quartus软件和Matlab软件并行开发。

3.1 相位累加器的实现

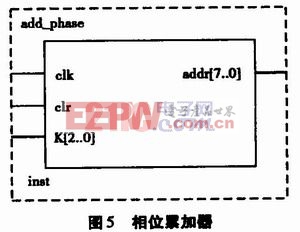

相位累加器主要用于产生ROM查询表所需的地址信息。图5为在Quartus软件中编程生成的相位累加器符号,相位累加器的输入信号包括时钟信号clk、复位信号clr和频率控制字K。输出信号addr[7…0]为ROM查询表的输入地址信号。

相位累加器类似一个计数器。首先,软件设置相位累加器的基数为0,并通过时钟信号clk上升沿触发,基数与频率控制字K相加,相加后的值反馈到相位累加器的输入端作为下一次的基数。当相位累加器的溢出时,—个完整的阶梯正弦信号就从ROM查询表的输出端输出。因此,相位累加器的溢出率就是正弦波信号的输出频率。相位累加器的仿真波形如图6所示。

评论