基于FPGA的信道化接收机

4 测试结果

系统输入测试信号为单频正弦信号,VPP为1 V,信号经过AD采样,DDC,信道化后,数据结果经过PCI上传给PC机作分析和显示。

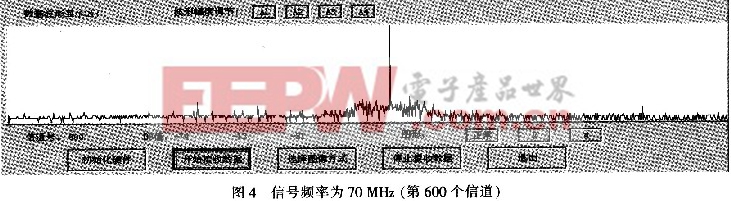

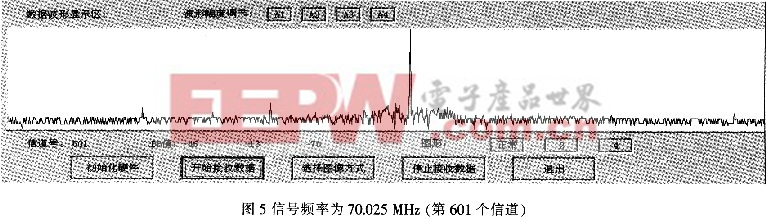

用Microsoft Visual C++6.0制作的界面中:横坐标是信道号,纵坐标是归一化功率值(dB),以数据形式显示的内容有:信号功率最大值对应的信道号、子信道输出相对于输入幅度的dB值以及相邻的两个信道的dB值。如图4和图5所示,输入信号频率分别为70 MHz,70.025 MHz,经过信道化后,在对应的信道号上都能输出谱线,频率分辨率达到25 kHz。经过多次重复测试,系统对相邻信道的带外抑制都达到55 dB以上。本文引用地址://m.amcfsurvey.com/article/191580.htm

5 结论

该系统主要器件包括AD6645、EP2S60,其中AD6654实现ADC,EP2S60负责系统控制、通信、算法实现,最终来实现了信道化接收功能。因此,该系统具有高度的灵活性和很强的通用性,可通过软件的重载或升级完成不同指标要求、不同模式的系统结构。在多板连接时,可以构成一个更大的阵列系统,可以用于DOA和DBF。

评论