不断演进的无源光网络(PON)需要FPGA设计的灵活性支

设计复杂性使成本问题更加严重。PONOLT和ONT拓扑结构是一个共享的媒体架构,这为系统OEM设计师提出了挑战。由于PON标准中采用了TDM技术,因此OLT和各个ONT之间的交互非常复杂。TDM用来共享不同驻地间的容量。早期的PON标准使用静态TDM,因此每个驻地接收相同的容量。

但是,最新的PON标准要求能够根据驻地的需求变化,为不同的驻地动态分配容量。这种动态带宽分配(DBA)功能需要利用ONT和OLT之间传送的信令通知OLT每个ONT所需的容量。OLT也需要将分配的容量通知给每个ONT。该协议基于从ONT到OLT的请求消息。OLT确定最佳的容量分配,并用确认消息予以响应。

另外,与较简单的点对点以太网端口不同的是,由于存在动态TDM要求,PON端口是一种更复杂的P2MP。因此OLT端口必须在多个ONT驻地之间进行连续切换。每个ONT分配得到32或64个可用时隙中的一个与OLT进行交互通信。OLT必须快速且连续地依次锁定到每个ONT数据流上,用的是众所周知的突发模式。为了支持这一极快的锁定方案,需要一个高度专用的媒体访问控制器(MAC)、串行/解串器(SerDes)以及时钟和数据恢复(CDR)功能。为了协调对每个ONT的访问,PON MAC尤其重要。本文引用地址://m.amcfsurvey.com/article/191611.htm

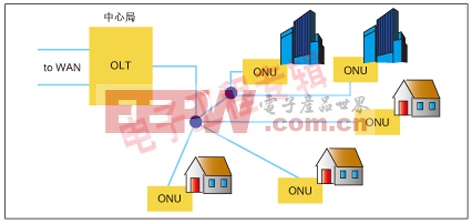

图1:DSL和PON拓扑共存。

基于FPGA的设计

针对上述背景,系统级OEM厂商在实现低成本和高效的OLT设计方面可选择性很少。一种方法是选用ASIC技术。但这种方法的投资成本极高。由于一些原因,ASSP也无法较好地实现。ASSP在支持PON演进需求方面的灵活性有限,缺乏设计可扩展性,并且功耗随着时钟速率的升高而升高。ASSP在提供可竞争的差异化产品方面的能力也很有限,还面临着器件停产的风险。另外,拥有成本也越来越高,上市时间较长。

然而,FPGA却能为OLT的设计提供低成本高效率的开发平台。当设计无缝移植到结构化ASIC进行大批量生产时成本还能进一步降低。这种方法由于省去了大型且耗时的ASIC开发,系统OEM厂商可以省去较大的成本,并缩短上市时间。

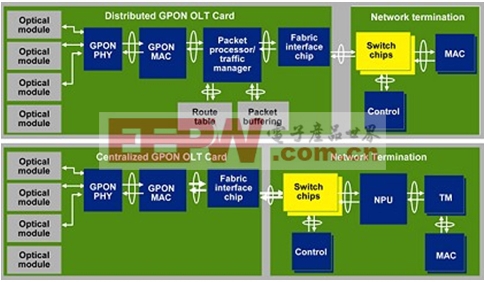

像Stratix这类FPGA器件,能够为实现和集成主要的OLT线路卡功能(见图2)提供所需的高性能逻辑。而且,FPGA也是用于实现CO OLT或者ONT用户驻地端EPON和GPON MAC的可选技术。另外,可以在一片FPGA中集成PHY和MAC,从而在一个芯片上实现虚拟线路卡。FPGA中先进的高效率内核矩阵基于的是被称为自适应逻辑模块(ALM)的创新逻辑单元。

图2:OLT线路卡采用的分布式与集中式架构的比较

评论