基于FPGA的PCI硬件加解密卡设计

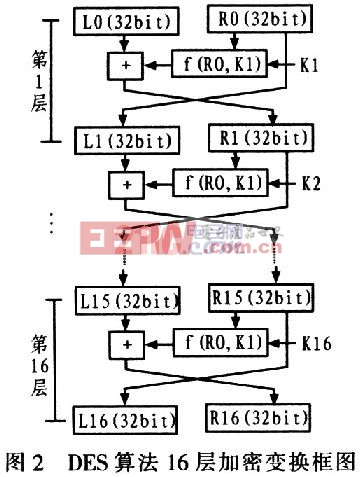

DES算法的加密过程分为4步:初始置换、迭代过程、子密钥生成和逆置换。DES算法16层加密变换框图如图2所示。本文引用地址://m.amcfsurvey.com/article/191636.htm

若采用时钟驱动级联式来实现DES算法,数据在时钟的驱动下从上一级的输出送入下一级循环的输入,那么对同一组数据完成加解密需要16轮时钟循环,至少需要16个时钟周期才能完成,加解密时间长。为了提高速度,采用了逻辑综合式进行DES设计。采用循环嵌套展开的方式完成16轮循环。利用编译综合器将16轮循环的整体逻辑结果用等效的逻辑电路来实现,当输入数据和密钥有效后,逻辑直接输出16轮循环的逻辑结果,使加密一组数据的时间由16个周期缩短为1个周期,时间延迟仅仅取决于电路的逻辑延迟。这种方法的缺点是占用了较多的系统资源,而且开发过程中不易做分级验证。

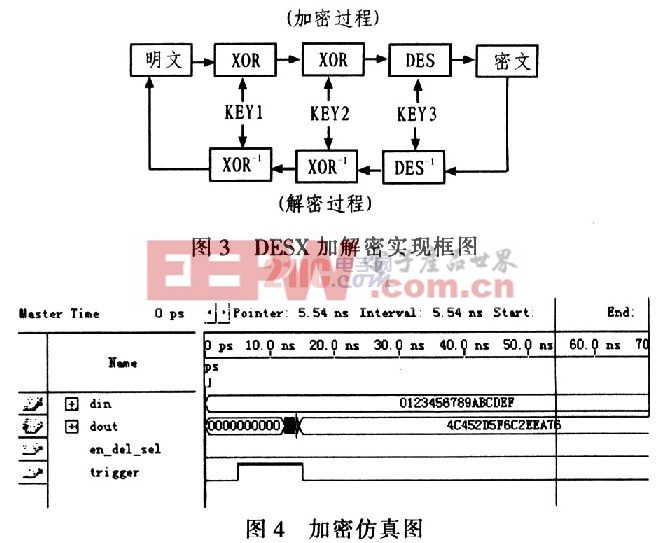

本系统使用的DESX算法是在DES基础上改进的加密算法。将DES的64位密钥扩展到192位,即使用3把64位的密钥。KEYl、KEY2和KEY3对数据块进行3次加密,充分保证了数据的安全。DESX加密过程分为3个步骤:1)使用KEYl对数据块做XOR运算;2)使用KEY2对上一步的结果再做XOR运算;3)使用KEY3对第二步的结果进行DES加密从而得到密文。与DES和3DES相比,只做一次DES运算。但密钥长度提高到192位,在保证安全性的前提下,最大限度提高了加解密的执行效率。DESX的解密过程与加密过程相反,其加解密流程如图3所示。图4是对数据0x0123456789-ABCDEF进行加密测试的仿真图,其系统时钟为50 MHz。

2.3PCI接口模块设计

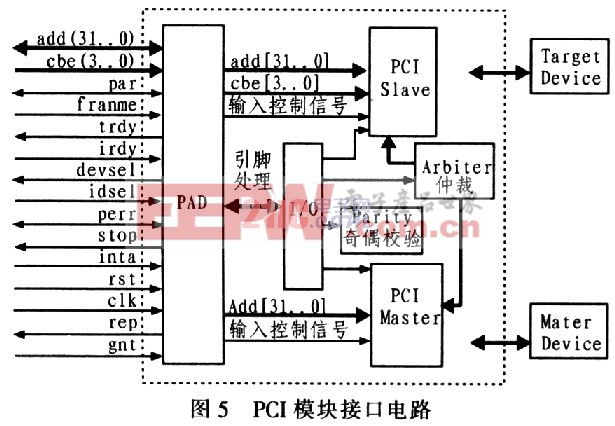

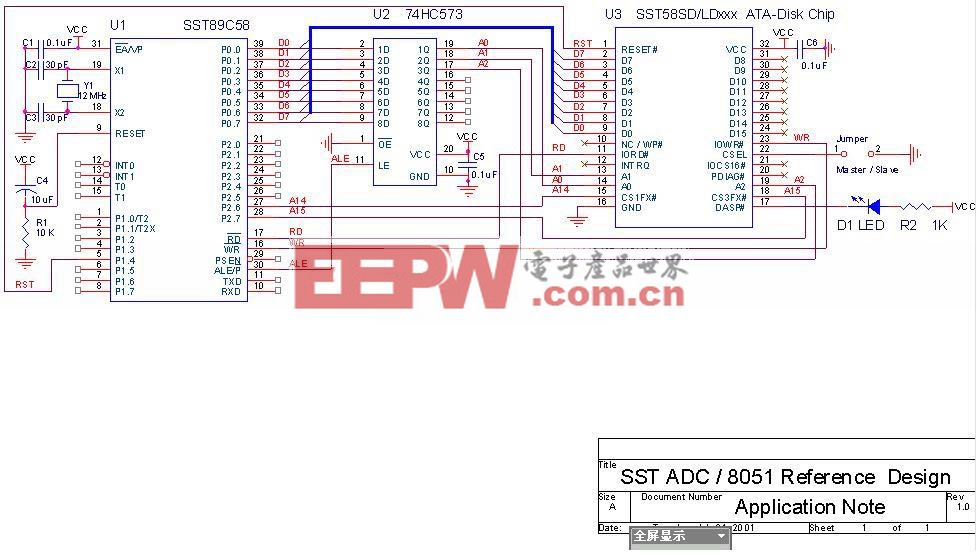

PCI接口模块是PCI总线与加解密卡之间的转换接口,也可认为其主要功能是起一个桥梁作用,完成用户设备与PCI总线之间的数据传输。从技术要求和成本方面考虑,以及本数据采集卡的特点,可以将加解密模块和PCI接口模块在一个FPGA内实现,用户可以按需要进行配置,而且提高了系统集成度,可移植性好。

PCI接口模块采用自顶而下的设计方法,在数据流和控制流分析的基础上,按照PCI接口的内部逻辑功能及结构,分成几个单独的模块,结构清晰,便于单独模块的测试。在设计PCI接口模块时,需要考虑支持PCI总线协议中的有关内容。PCI接口模块可以只包含PCI-Slave(从PCI),也可以选择同时包含PCI-Mater(主PCI)。其中,PCI-Slave是接口模块必须的,PCI-Mater是可选的,但是如果实现PCI-Mater,则Arbiter(仲裁器)就是必须的。完整的PCI接口模块电路如图5所示。

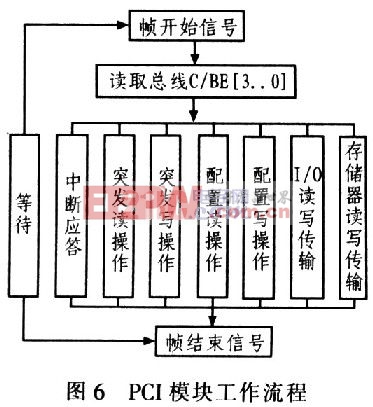

PCI接口模块的核心设计分为时序控制和配置空间两部分。时序控制部分保证了板卡能按正常的PCI时序工作,配置空间部分保证了PCI卡的即插即用功能。在时序控制程序中采用状态机模型来实现不同时序的转换,各种命令、数据交换、控制均在状态机的管理下进行工作。本设计中的状态机主要由中断应答、突发读操作、突发写操作、配置读操作、配置写操作、I/O读写传输、存储器读写传输等7个部分组成,工作流程如图6所示。

超级电容器相关文章:超级电容器原理

评论