基于DSP和FPGA的实时图像压缩系统设计

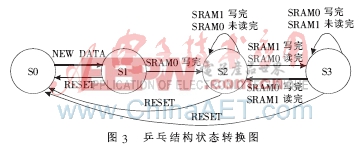

乒乓控制模块按照功能还分为:S0、S1、S2、S3 4个转换状态。其中,状态S0为初始化状态(所有信号都处于初始化状态),系统加电或者复位后进入此状态;在S1状态,主要负责对SRAM0的写入,不可以对SRAM1进行读操作;在S2状态,主要负责对SRAM1进行写操作,对SRAM0进行读操作,当SRAM1写完后,如果SRAM0未读完,则继续处于状态S2,如果SRAM0读完,则进入状态S3;在S3状态,主要负责对SRAM0进行写操作,对SRAM1进行读操作,当SRAM0写完后,如果SRAM1未读完,则继续处于状态S3,如果SRAM1读完,则进入状态S2。乒乓控制模块状态转换图如图3所示。本文引用地址://m.amcfsurvey.com/article/191641.htm

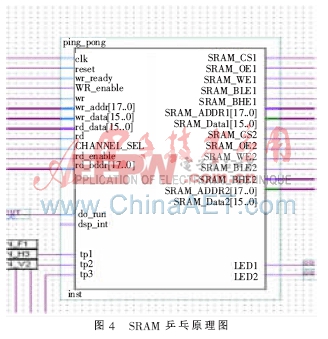

SRAM乒乓电路如图4所示。图中,wr_data为Camera Link接口接收到的只包含灰度信号的图像数据。为了方便图像数据的管理,每个像素、每行的像素都对应到了SRAM的固定地址,所以wr_addr为该像素在SRAM中的地址,同时也可以表示该像素在一幅图像中的位置。CHANNEL_SEL为读SRAM的标志位,0代表SRAM0,1代表SRAM1。

2.3 FIFO缓存模块和RS422传输模块

由于DSP向RS422模块传输数据并不是匀速传输,而且传输速度比RS422的传输速度快很多倍,所以必须采用FIFO模块。

3DSP程序设计

TI公司的TMS320DM642芯片是一款高性能视频处理器,其主频可以高达600 MHz,数字处理能力可以达到4 800 MI/ps[3]。

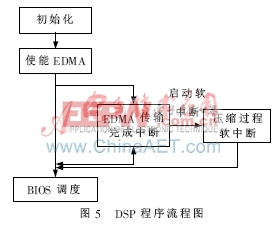

DSP工作流程图如图5所示,DSP在相关外设与EDMA相关寄存器初始化完成后,才开始响应中断事件触发EDMA传输,在本系统中由EXITUINT4中断上升沿触发EDMA进行传输。在接收到FPGA发送的中断信号后,开始进行EDMA传输,整个EDMA传输的过程需要10 ms左右,传输完成后触发EDMA中断,在中断服务函数中触发1个软中断,在软中断服务函数中进行图像数据的压缩。

3.1 EDMA乒乓程序设计

在整个DSP的工作流程中,要实现图像数据采集、压缩、传输同时进行,则在DSP程序中需要1个双缓冲buffer,在向buf1中采集图像信号的时候,DSP可以对buf2中的数据进行压缩,而在对buf2中进行采集的时候,DSP可以对buf1中的数据进行压缩。

评论