基于FPGA的移位寄存器流水线结构FFT处理器设计与实

对于移位寄存器,在实现时,各级的前级移位寄存器深度为N/2-1,从本质而言,是使运算开始的时钟上升沿到来时,数据已经出现在碟算模块输入线上,而不需要下一个时钟的驱动来移出寄存器,比如第二级移位寄存器的级数为63。这样,运算周期正好是2的倍数,从而方便使用计数器的各位直接对开关进行控制。

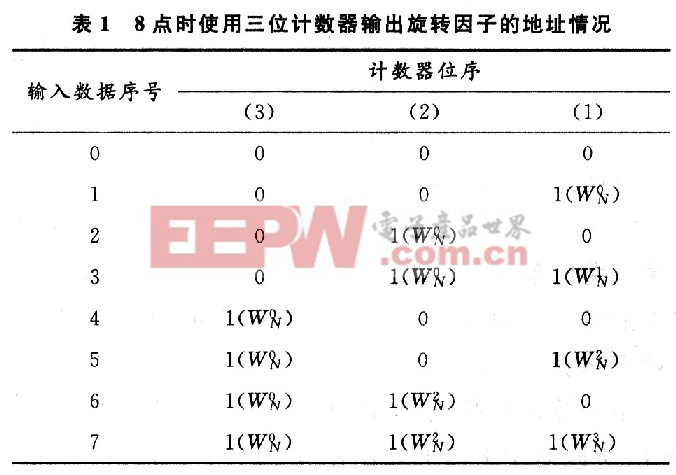

同时,计数器还可以用来产生所需旋转因子的RAM地址。根据各级蝶形运算所需旋转因子的规律,可以利用计数器的高位补零来产生查找表的地址。比如,对于第一级,因为需要在最低位第一次出现1时提供

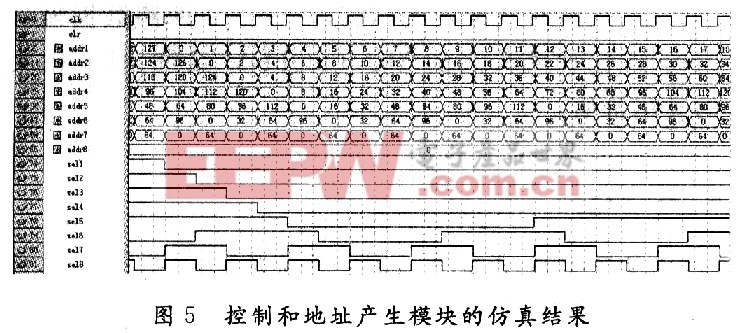

控制和地址产生模块的仿真结果如图5所示,其中sel代表开关控制,addr代表产生的地址。

3.2 蝶形运算模块

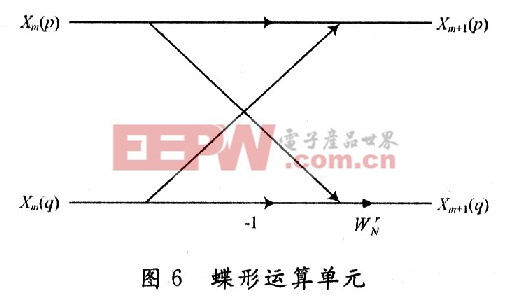

蝶算模块由一个复数加法器,一个复数减法器和一个旋转因子的复数乘法器构成,如图6所示。

旋转因子乘法器通常由4次实数乘法和2次加/减法运算实现,但因为cos和sin的值可以预先存储,通过下面的算法可以简化复数乘法器:

(1)存储如下三个系数:C,C+S,C-S

(2)计算:E=X-Y和Z=C*E=C*(X-Y)

(3)用R=(C-S)*Y+Z,I=(C+S)*X-Z,

得到需要的结果。

这种算法使用了3次乘法,1次加法和2次减法,但是需要使用存储3个表的ROM资源。

设计中数据的输入为16位复数,所以将旋转因子cos(2kπ/N),sin(2kπ/N)量化成带符号数的16位二进制数后,存储到ROM中,由于值域不同,需要注意C+S和C-S的表要比C表多1位精度。

运算后的结果需要除以量化时乘以的倍数16b011111llllllllll。具体实现时由于除法运算在FPGA器件需要消耗较多的资源,设计中采用二进制数移位的方法来实现除法运算。为了防止数据溢出,设计对输出结果除以2。图7为蝶形运算模块的RTL级结构图。

评论