低功耗FPGA电子系统优化方法

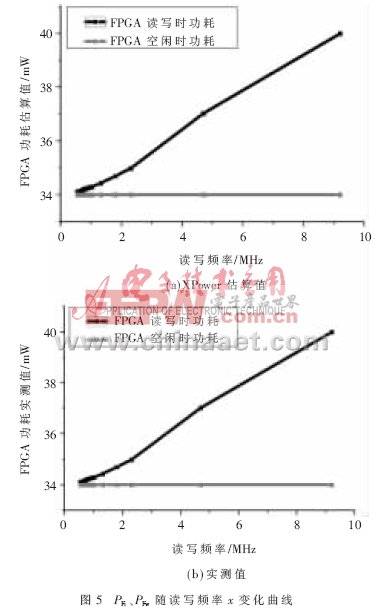

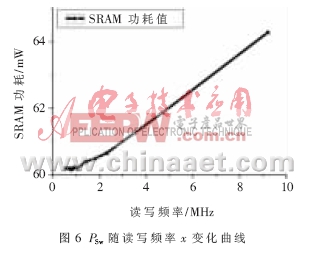

图5(a)为PFw、PFi的估算值,图5(b)为测量值,其中黑线为PFw,灰线为PFi。图6为测得的PSw值。由于y为读写时间占空比,所以(1-y)为系统空闲时间占空比,故系统平均功耗P为:

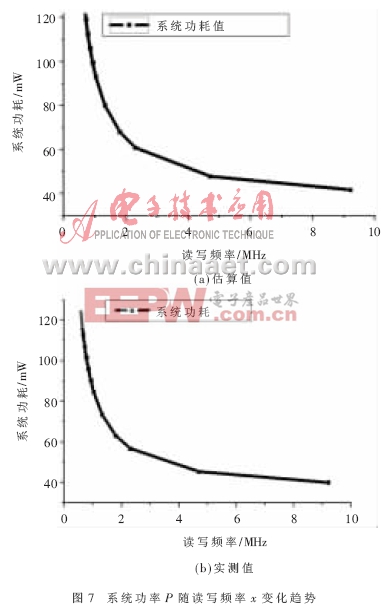

P=(PFw+PSw)・y+PFi(1-y) (2)

又:y=6 kHz/x MHz (3)

由(2)、(3)式和图5、图6中的数据,可得P关于x的曲线图,如图7所示。本文引用地址://m.amcfsurvey.com/article/191793.htm

通过对比估算值与实测值发现,估算值与实测值曲线基本吻合,它们的最小点都出现在x为9 MHz处。

由以上结果可知,当读写频率与读写时间占空比不同时,系统整体功耗是有差距的。系统采用(9 MHz,6.7×10-4)的参数是最省功耗的,即系统每秒钟以9 MHz频率工作6.7×10-4s,其余时间空闲,比系统用其他读写频率和读写时间占空比的平均功耗要小。在所取样点中,最小功耗值比样点中的平均功耗值节约了10%左右的功耗,可见此方法在现实设计中可以很好地对系统功耗进行优化。

对电子系统来说,减少功耗可以带来很多好处,除了简化系统的散热处理及系统集成方面的工序、节约成本外,还能提高系统可靠性、降低热噪声干扰等。对便携式仪器、野外工作仪器等电池供电的系统来说,还能延长电池寿命,减少更换电池的麻烦。

评论