基于CPCI总线的通用FPGA信号处理板的设计

2 通用FPGA信号处理板的在某雷达系统中的应用

2.1 通用信号处理板实现数字下变频

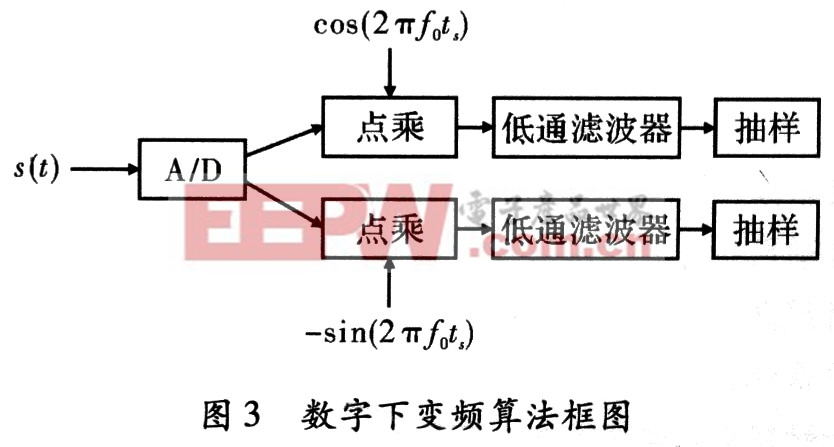

数字下变频是雷达信号处理中的关键技术之一,通常采用低通滤波法来实现数字下变频,低通滤波法包括正交插值、低通滤波和抽样3个部分。数字下变频的算法框图,如图3所示。模拟信号经过A/D正交采样后分别与余弦模块和正弦模块进行点乘,实现正交变换,然后I、Q两路数据各自经过低通滤波器,最后抽样输出。

图4为数字下变频算法的FPGA实现框图,主要分为3模块:数据转换模块、FIR模块和抽样模块,其中数据转换模块实现乘法运算,当外部数据进来时根据不同时刻输出不同的数据,主要包括原值、原值取反和0。

输入时宽带宽积为1 028的线性调频信号,系统实测I路Q路波形,如图5所示。

2.2 通用FPGA信号处理板实现大时宽带宽积数字脉冲压缩

数字脉冲压缩(Digital Pulse Compression,DPC)处理是指对雷达接收机接收的雷达回波经过A/D采样后,对数字信号进行脉冲压缩处理。数字脉冲压缩的实现可分为两种:时域法和频域法。时域处理是指雷达回波序列x(n)与匹配滤波器的系数h(n)做卷积运算。此时匹配滤波器的输出为

参与脉冲压缩的信号和匹配参数都是复数,因而时域处理是一个复数卷积过程,卷积过程也就是乘一累加(Multiply-Accmulate,MAC)的过程。

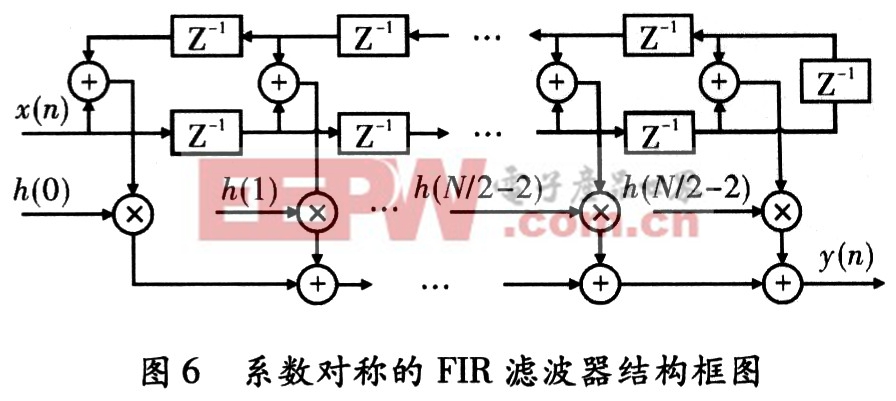

对于脉冲压缩系统而言,通常需要处理线性调频信号、非线性调频信号。对线性调频和非线性调频信号,其匹配滤波器系数均可设计成对称形式,通过使用对称结构的FIR滤波器结构,在数据和系数相乘之前,完成数据的相加,乘法的运算量减少N/2次,大大节省了乘法器资源。结构框图,如图6所示。

由于FPGA中乘法器资源非常宝贵,为了提高乘法器资源的利用率,采用时分复用的方法,考虑只用一个乘法器,对其进行时分复用。在不需要较高采样速率的系统中,这种结构可以做到实用高的性价比。在设计滤波器时,根据实际情况灵活地选择乘法器的复用次数Ⅳ和采样频率。从上次加法运算结束到这次加法运算开始的时间间隔内,乘法器应完成N次乘法运算,也就是实现了一次卷积运算,这样就只需要一个乘法器,其时序关系,如图7所示。

时分复用结构框图,如图8所示。

根据FPGA的速度等级和数据的采样频率,选择乘法器的复用次数为40。利用StratixⅢ的专用增强型锁相环(Enhanced PLL)的倍频功能,生成一个40倍采样频率的时钟作为乘法器的时钟,使乘法器在一个稳定的数据周期内完成40次乘法运算。每40阶作为一个乘累加单元,分别处理,最后对各单元结果求和。每个单元使用两个40选1的选择器,一个选择参与运算的数据,另一个选择参与运算的相应匹配系数,数据和系数同时送到乘法器内,完成运算后,送到累加器中,每完成40次乘法,锁存累加结果yk(n),各级的yk(n)相加,得到最终的脉压结果y(n)。通过时分复用技术,乘法器的数量只需原来的1/40。

评论