基于FPGA的高速时钟数据恢复电路的实现

2.4 数据恢复

由于时钟数据恢复电路的目的就是得到能够正确采样输入数据的时钟信号。为了保证恢复出的时钟和输入数据的相位关系在整个芯片内都能够成立,在系统应用中输入信号也走全局时钟网络。经过这样处理后,只要在需要恢复数据的地方加一个D触发器即可得到正确的数据信号。本文引用地址://m.amcfsurvey.com/article/191906.htm

3 环路仿真结果及讨论

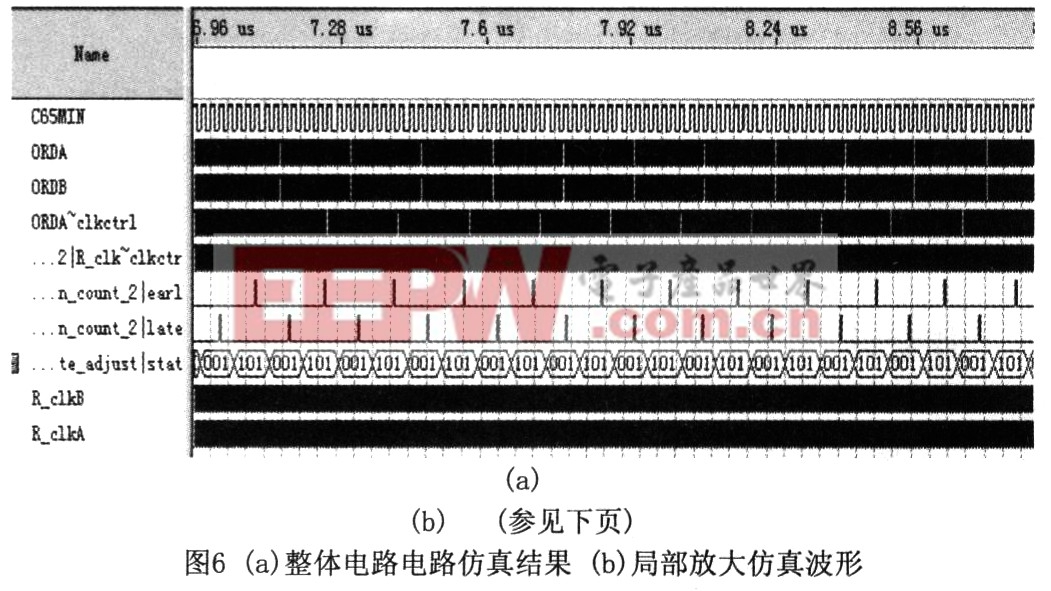

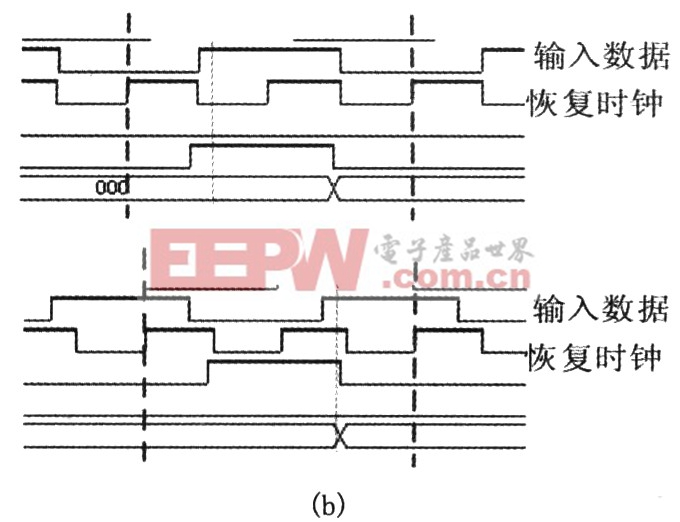

采用EP2C5T144C6器件的环路的仿真结果如图6所示,其中工作频率为204.8MHz。由于整个电路用的是经过全局时钟控制模块后的时钟和输入数据,所以在图6中给出的是这两个信号时序关系:ORDA~clkctrl和R_clk~clkctrl。由图(a)及局部放大图(b)可以看出,电路稳定时钟信号在输入数据的中间位置左右摆动,可以正确采样输入数据。

本文提出的电路结构不需要高频时钟信号,因此只要相位调整过程中时钟信号的脉冲宽度大于器件要求的最小值,且满足整个电路满足建立保持时间就可以正常工作。因此最小的时钟周期T=max(3*Tmin,Tper),其中Tmin是所用器件时钟信号脉冲宽度的最小值,Tper是满足建立保持时间的最小时钟周期。例如EP2C35F672C6芯片工作时钟高电平脉冲最小值为1ns,采用该芯片电路的工作频率可以达到300MHz,这个工作频率已经通过了Altera DE2板的硬件验证。如果采用更快的器件如Cyclone III EP3C10T144C7,时钟脉冲宽度最小值0.625ns,经过仿真验证其工作频率可以达到400MHz。在时钟调整模块后加一个简单的二分频电路,就可以实现12个时钟相位的调整精度,根据不同器件的性能很容易进行扩展,达到所需要的设计要求。

4 结论

本文利用时钟切换的方法,在低端AlteraEP2C5T144C6上实现了204.8MHZ的时钟数据恢复电路,并通过了硬件验证。通过理论分析给出了决定该电路工作频率的主要因素,同时对该电路稍加改动就可以实现更高精度的时钟数据恢复电路,具有很好的扩展性,为利用中低端FPGA实现高速通信系统提供了一种可参考的解决方案。

评论