基于CPLD的异步串行收发器设计

关键词:异步串行收发器;混合输入;在系统可编程;CPLD;ispLSI1016

传统数字系统的设计主要基于标准逻辑器件并采用“Bottom-Up”(自底向上)的方法构成系统。这种“试凑法”设计无固定套路可寻,主要凭借设计者的经验。所设计的数字系统虽然不乏构思巧妙者,但往往要用很多标准器件,而且系统布线复杂,体积功耗大,可靠性差,相互交流和查错修改不便,设计周期也长。随着电子技术的发展,采用先进的CPLD ?复杂的可编程逻辑器件?器件取代传统电路已经成为技术发展的必然趋势。Lattice公司的ispLSI是当今世界上速度最快密度最高的CPLD之一。它采用先进的ISP技术,使器件无需拆卸即可在系统内重新配置逻辑功能。数字系统设计的革命性变化,使得传统的“固定功能集成块+连线”的设计方法正逐步退出历史舞台,而基于芯片的设计正在成为电子系统设计方法的主流。

本设计选用Lattice公司生产的ispLSI1016器件,并以“异步串行收发器”为例,采用现代电路与系统中的设计思想来说明“基于芯片的设计”在实现数字系统的具体应用方法。这种设计方法不仅可使硬件设计“软件化”、缩短设计周期、提高效率,而且易于修改和“升级”。

1 异步串行收发器的工作原理

异步串行收发器的工作原理主要包括两部分:第一是接收串行数据并将其转化为并行数据,第二是把并行数据以串行数据方式发送出去。由于接收和发送是异步的,所以接收部分和发送部分需要不同的时钟。

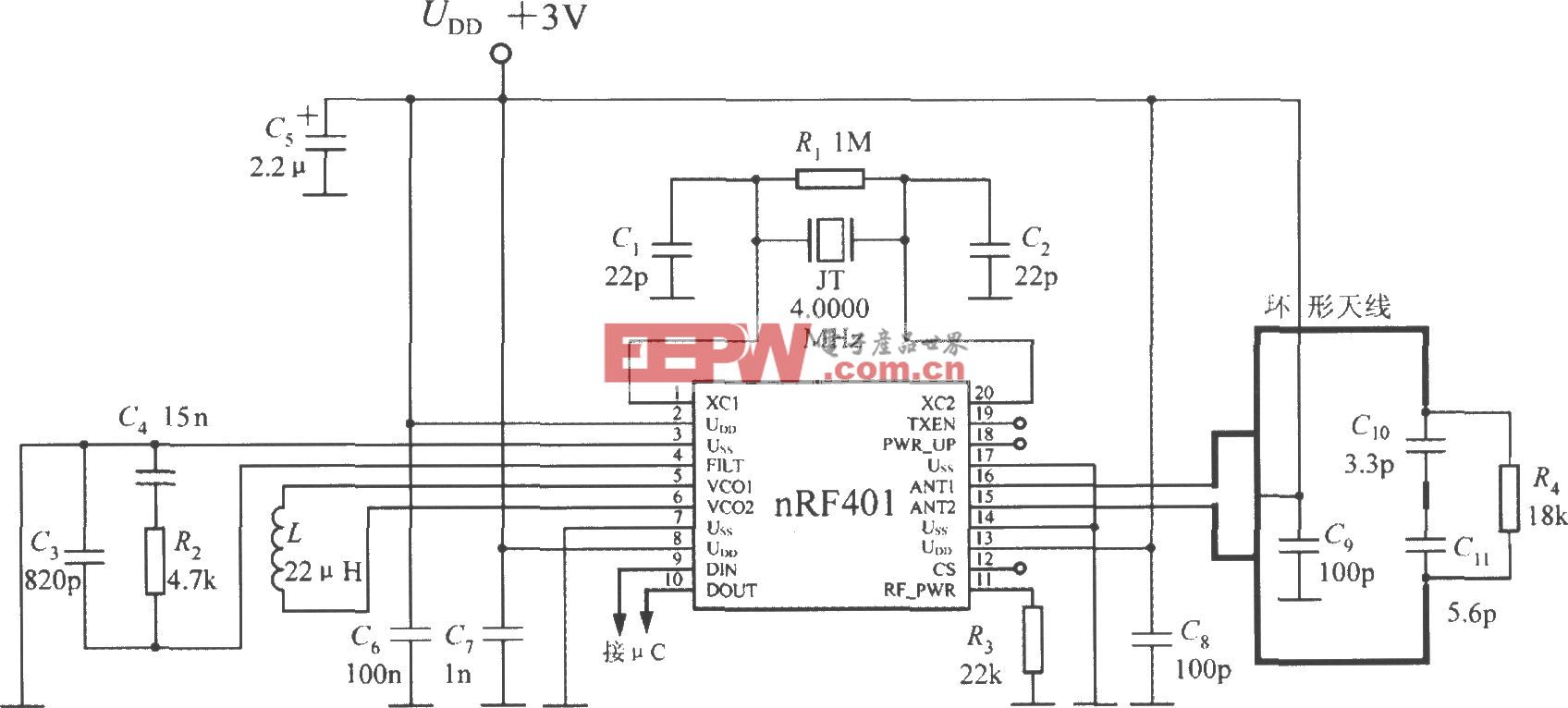

发送部分的系统工作原理如图1所示,其中TXD?7?0?是并行数据输入信号,TBITCLK是发送器时钟信号,RESETF是发送器控制模块内部复位信号,MWDSLF是电平敏感锁存器使能信号,TRSTF是一位锁存器模块复位信号,TXDATA是串行数据输出信号。

当发送电路工作时,电平敏感锁存器使能信号(MWDSLF)有效,并行数据被送入锁存器,之后,控制模块1产生并入串出移位寄存器装入信号(STLD),以在时钟信号(TBITCLK)的作用下,将并行数据装入并入串出移位寄存器,然后,控制模块1再产生并入串出移位寄存器移位信号(STLD),并在时钟信号(TBITCLK)的作用下,将并行数据移出。

接收部分的系统工作原理如图2所示,其中RXDATA是串行数据输入信号,RBITCLK是接收器时钟信号,RE-SETF是接收器控制模块内部复位信号,MRDSLF为边沿触发锁存器使能信号,RXD?7:0?是并行数据输出信号,RDRDYF是并行数据准备好信号。该部分电路工作时,首先在时钟信号(RBITCLK)的作用下,串行数据(RXDATA)被串入并出移位寄存器转化为并行数据;同时,控制模块2在行计数控制下,在一帧串行数据到并行数据转换完成时,使边沿触发锁存器使能信号MRDSLF有效;之后,在控制模块产生的时钟信号的作用下将并行数据锁存到锁存器,同时,使并行数据准备好信号(RDRDYF)有效。

2 异步串行收发器的具体实现

硬件电路功能来用Lattice公司的CPLD来实现,用ispLEVER3.0 进行软件设计。可利用原理图和硬件描述语言VHDL完成源文件的设计。以下对其CPLD流程源文件及仿真波形作以介绍。

2.1 用ispLEVER软件设计CPLD的流程

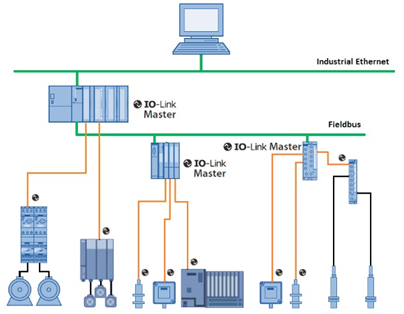

Lattice公司新的设计工具ispLEVER可支持isp-MACH、 ispLSI、 ispGDX、 ispGAL、 GAL器件以及具有革新意义的新的ispMACH 5000VG和ispMACH 4000 CPLD器件系列。用ispLEVER设计CPLD的源文件主要有硬件描述语言(VHDL、Verilog HDL和ABLE-HDL)、电路原理图和网表五种方式。在利用该软件设计数字电路与系统时,可采用原理图、硬件描述语言以及混合输入方式。本设计将采用混合输入方式(原理图与VHDL语言)。用ispLEVER软件设计CPLD的基本流程如图3所示。

2.2 源文件输入

ispLEVER软件的系统库包括3部分:可编程大规模集成电路库(pLSI)、通用电路库(GENERIC)、用户自己设计的元件库(Local)。这些库中又列出了若干子库,而这些子库都是以宏来定义的,如门(Gate)、寄存器(Regs)、算术运算器(Ariths)、I/O端口等。

在原理图输入方式中,首先应当用这些宏来构成电路符号,然后像逻辑元件那样画成原理图,同时给出它们的连线以及各个输入输出缓冲器电路的具体配置。由此构成的宏在原理图上只是一些方框形的符号,没有涉及其内部具体逻辑,因而这种宏实际上是一种所谓的顶层原理图。与顶层原理图对应的是底层原理图,顶层原理图实际上是一种由各种门和触发器等基本逻辑器件组成的基本原理图,可以说它是顶层原理图的内核。除了直接用基本逻辑器件构成底层原理图外,还可以用硬件描述语言编写源文件模块以作为宏,同时作为一种底层原理图去充实、支持顶层原理图。顶层模块原理图如图4所示。

顶层宏模块中发送器部分?TRANSMITTERM_S?的原理图如图5所示,电平锁存器、一位锁存器模块以及控制模块1部分可调用系统库内的宏模块,因为这一部分硬件电路已很成熟,而且并不是很复杂。调用库内宏模块用相对于硬件描述语言而言,其占用系统资源较少。

图5中,圆圈部分的并入串出移位寄存器(PS_SHIFTREG)宏模块可用硬件描述语言(VHDL)进行功能描述。其VHDL源文件如下:

LIBRARY ieee;

USE ieee.std logic 1164.ALL;

entity logic166 is

Port ? A ? In std logic;

B ? In std logic;

C ? In std logic;

CLK ? In std logic;

D ? In std logic;

E ? In std logic;

F ? In std logic;

G ? In std logic;

H ? In std logic;

SER ? In std logic;

STLD ? In std logic;

QH ? Out std logic ?;

end logic166;

architecture BEHAVIORAL of logic166 is

signal t latch? std logic vector?7 downto 0?;

begin

process?STLD,CLK,SER,A,B,C,D,E,F,G,H?

begin

if?CLK'event and CLK=′1′? then

if?STLD=′1′? then

t latch?7?<=A;

t latch?6?<=B;

t latch?5?<=C;

t latch?4?<=D;

t latch?3?<=E;

t latch?2?<=F;

t latch?1?<=G;

t latch?0?<=H;

else

t latch?0?<=t latch?1?;

t latch?1?<=t latch?2?;

t latch?2?<=t latch?3?;

t latch?3?<=t latch?4?;

t latch?4?<=t latch?5?;

t latch?5?<=t latch?6?;

t latch?6?<=t latch?7?;

t latch?7?<=SER;

end if;

end if;

end process

QH<=t latch?0?;

end BEHAVIORAL;

图5

顶层宏模块中接收器部分?RECEIVER_S?的原理图如图6所示,边沿触发锁存器、串入并出移位寄存器以及控制模块2部分可以调用系统库内的宏模块。图中圆圈部分的计数器(COUNTER9)宏模块可用硬件描述语言(VHDL)进行功能描述。VHDL源文件如下:

LIBRARY vanmacro;

USE vanmacro.components.ALL;

LIBRARY ieee;

LIBRARY generics;

USE ieee.std logic 1164.ALL;

USE ieee.numeric std.ALL;

USE generics.components.ALL;

entity counter9 is

Port ? clk ? In std logic;

cao ? Out std logic ?;

end counter9;

architecture behav of counter9 is

signal counter? integer range 0 to 9;

begin

process?clk?

begin

图6

if?clk'event and clk=′0′? then

if?counter=9? then

counter<=0;

else

counter<=counter+1;

end if;

end if;

end process;

process?counter?

begin

if?counter=9? then

cao<=′1′;

else

cao<=′0′;

end if;

end process;

end behav;

在上述源文件设计中,控制模块1和控制模块2都采用了调用宏模块的方式。在此设计中,时序控制十分重要,而采用调用宏模块的原理图输入方式能很好的控制延时参数。如果用硬件描述语言进行时序功能描述,那么经逻辑综合、优化后,其延时参数有时很难控制。而减小延时参数需要更多的资源来补偿。

2.3 仿真分析

ispLEVER软件提供了强大的功能仿真和时序仿真功能,其最高仿真频率可达36MHz。图7是接收器部分的仿真波形。预接收的串行数据为:“10101110”。而发送器部分的仿真波形如图8所示。预发送的并行数据为:TXD0=‘1’,TXD1=‘0’,TXD2=‘1’,TXD3=‘0’,TXD4=‘1’,TXD5=‘1’,TXD6=‘1’,TXD7=‘0’。

3 结论

该设计充分体现了ISP技术的优越性,使整个系统无论从最初方案的设计到编写程序,还是从仿真调试到下载验证,都显得相当快捷和方便。采用ISP技术具有流程简单、无引脚损伤、可实现多功能硬件、并可为测试重构逻辑等优点。随着网络技术的日益完善,通过网络来对远隔万里的用户系统进行软件版本的升级换代,无疑会给厂家与用户带来更多方便。该异步串行收发器接收和发送的bit数可根据具体需要进行相应的改动,而且只需改动底层模块中的锁存器、串入并出移位寄存器及并入串出移位寄存器的bit数和计数器的大小(控制模块部分不需改动),然后再经相关软件的综合和适配,即可重新下载到具体器件中。该设计中 bit数选择8位,完全是出于所选器件的容量考虑。

评论