基于MAX1452的应变测试系统前端模块的设计

2.2 单通道应变采集电路硬件实现

根据MAX1452芯片特性可知,MAX1452对外部传感器提供了可编程的电压源激励或电流源激励。当对外部传感器供电时,要求外部传感器供电满足片上激励源输出电流或者电压的限制条件。考虑到本次开发的应变测试系统使用的传感器应变电桥是350 Ω阻抗,当提供+5 V电压激励时,需要提供大约14 mA的电流,而MAX1452仅能提供最大2.5 mA的电流,因此需要增强其电流驱动能力。同时,MAX1452适应于输出灵敏度为4 mV/V到60 mV/V的传感器,而本系统中应变电桥在测量最小范围1 000μs时,10 V供电才产生5mV的输出电压信号,因此在MAX1452和应变电桥之间尚需要一高精度差分放大器进行预放大。

MAX1452内部的4个16位DAC模块的基准都来自于它的电源引脚VDD,因此其供电电压的精度对性能的影响很大,这里采用了一个高性能电压基准芯片MAX15006B将+12 V供电电压转换为高精度的+5 V电压,为MAX1452及其它芯片提供一个稳定电源与基准电压。值得注意的是,此处系统电路硬件和软件设计仅仅在工作模式上使用了处于非比例工作电路的MAX1452的数字模式,在温度修正方面使用了一阶线性温度修正功能,而并没有考虑MAX1452的其他工作模式。

MAX1452通过一个双向的引脚DI/O与微控制器交换数据,它们之间进行通信的协议是异步串行通讯。当主机发送初始化序列时,MAX1452将自动检测主机的波特率。无论MAX1452内部震荡器如何设置,使用4 800 bps与38 400 bps之间的波特率都可以检测得到。数据格式为始终为1个起始位、8个数据位、1个停止位,没有奇偶校验位。引脚UNLOCK一个功能是控制MAX1452与微机通信的状态:当其为低电平时,禁止MAX 1452与微控制器进行通讯。引脚UNLOCK的另一个功能是配合加密锁控制寄存器(即CL[7:0])对MAX1452的工作模式进行设置,此处没有使用该模式,仅将其连接到微控制器的一个通用I/O口上即可。CLK1M引脚通过配置寄存器向外部提供一个标准的1 MHz的时钟信号以供外部控制器使用,可以减少外部震荡电路的设计;当不需要使用该信号时,也可以通过配置寄存器关闭该时钟信号的输出,以降低EMC干扰。

3 系统软件设计

系统软件设计主要包括MAX1452集成芯片固件驱动程序设计和整个采集模块系统控制程序的设计2大部分。这里我们使用的是大规模可编程逻辑FPGA芯片实现的。开发使用的语言采用了Verilog HDL硬件描述语言,开发环境是QualtusII软件的10.1版本。由于FPGA控制器和MAX 1452进行通信的软件设计是本次软件开发的难点和重点,本文以下对其详细介绍。

FPGA控制器与MAX1452的通讯采用了异步串行通信协议,需要使用一个双向数据线实现数据的输入输出。FPGA可以使用一个通用的双向I/O引脚来模拟异步串行异步通信,也可以利用大部分微控制器上集成的异步串行通讯接口来(如当前通用的C51系列单片机或ARM芯片等)实现。本次应变测试系统的设计利用了微控制器内部集成的异步通讯外设(波特率需要设置在4 800 bps与38 400 bps之间,数据格式要设置为1个起始位、8个数据位、1个停止位,无奇偶校验位)来实现对MAX1452的寄存器进行读写控制。

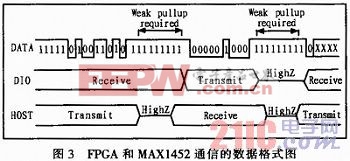

当MAX1452工作在数字模式下(本次设计即采用了这种模式),FPGA要通过串行接口命令来加载寄存器数值(包括了DAC数据寄存器和配置寄存器等),对内部的EEPROM进行擦除或数据加载,或者读取MAX1452内嵌的温度传感器的数值。实现的步骤依次是在稳定电源给器件供电1 mS后,首先发送一个初始化序列字节(0x01h),如果必要的话还需要发送一个重新初始化系列字节(0xFFh);其次按照IRS(接口寄存器集)确定的格式(见参考文献)对所有寄存器、EEPROM单元和温度索引值进行读写访问。微控制器访问MAX1452的数据格式图3所示。本文引用地址://m.amcfsurvey.com/article/194441.htm

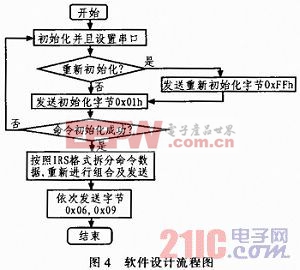

微控制器通过MAX1452对传感器芯片进行调理的过程其实就是不断地对MAX1452内部各种不同用途寄存器进行读写访问的过程。通过上面的说明我们可以看到读写寄存器不仅需要通讯格式命令,还需要按照IRS格式不断进行拆分字节和组合字节,这里我们给出微控制器访问配置寄存器的程序流程图,如图4所示,以便读者更加清楚了解。

4 结论

文中通过上述系统的软硬件设计,实现了网络化应变测试系统中前端电路采集模块的设计,满足了网络化应变测试系统中对前端采集模块设计中所要求的特点。采用这种集成的传感器信号调理芯片的设计方案在进行飞行试验的实际应用中具有采集精度高,体积和供号小,可以按照要求分布式安装在飞机各个空间狭小的部位,达到了预期的设计目的。

评论