嵌入式脉象采集仪电路设计

摘要:该脉象采集仪采用IP核技术、SoPC技术,将脉象采集的大部分功能都集成在一片FPGA内部,并自主进行了脉象采集控制的FPGA 设计。该设计采用在SoPC系统外做控制电路部分,三路脉搏信号共用一个ADC,只需要很少的外部器件就能实现。与早期采用工控机、PC机,或者现在多采用的ARM设计方法相比,该脉象采集仪具有成本低,功耗低,体积小,便于扩展,稳定性高和系统维护方便等优点。

关键词:脉象采集;FPGA;IP核;嵌入式系统

脉诊作为中医最重要的一种诊断方式,具有模糊性、不确定性的特点,是近年来中医现代化研究中的热点。随着电子、计算机技术的快速进步,将嵌入式技术、 FPGA技术、IP核技术结合在一起,融合电子技术、信号处理方法等学科知识,在中医基本理论的指导下,设计脉象诊断设备,构建一个灵活高效,可扩展性强,可靠性高,功耗低,可便携的脉象采集仪具有重要的现实意义和良好的市场前景。

1 仪器总体设计

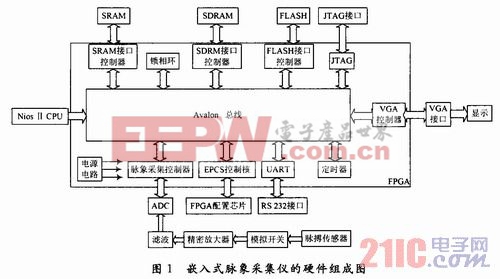

嵌入式脉象采集仪的前期设计目标是脉搏信号的采集、存储、显示、简单处理、通信等,后期要对所采集到的信号处理,得到脉象特征,对病人做出诊断。在 FPGA的选型时,不但要考虑当前功能是否够用,价格适中,而且要考虑产品的升级换代,所以设计的系统选择Alt-era公司Cyclone II系列EP2C35F484C8作为核心芯片。以FPGA芯片为核心的嵌入式脉象采集仪的结构组成如图1所示。从图1中可以看出,硬件主要由电源、显示、存储器、脉象采集、FPGA、通信等6个模块组成。

2 主要外围电路设计

由于在FPGA内部采用VGA控制器IP核,选择模拟仪器公司的10位高速视频DAC芯片。

SRAM采用IDT公司的IDT71V416器件,利用2片IDT71V416器件构成32位存储器,以与NiosⅡ的32位CPU的总线匹配。对 SRAM的控制,选用Altera公司提供SRAM控制器核,其控制信号由SoPC自动生成。SDRAM为系统中的数据及堆栈提供暂存空间。系统启动后,程序代码调入SDRAM中运行,以提高系统的运行速度。系统中采用HYNIX公司的64 MB SDRAM,型号为HY57V561620HT。它提供LVTTL接口,分为4个BANK,每个BANK容量为4 M×16 b。由BA0,BA1的状态决定选定那个BANK。FLASH存储器的设计采用AMD公司的AM29LV128M器件。可以自由选择数据的位数为16 b或者8 b,但是最高位是模式位,采用IP核完成设计,具有比较优越的性能。

2.1 通信模块的设计

采用非常普遍的串行口通信。RS 232串行总线具有结构简易,成本低廉,硬软件支持丰富,安装方便等特点。虽然RS 232的速度稍微慢了点,但是对于频率小于100 Hz信号的采集还是足能满足的。采用MAXIM公司的max3232作为串口转换芯片,其供电电压为3~5V,速度可以达到1 Mb/s,具有良好的性能。

2.2 脉象采集模块的设计

脉象采集模块包括传感器、仪器放大器、采样保持器、A/D转换器等,是脉象采集仪的关键部分。

脉象采集仪的传感器决定着采集的质量,设计采用硬面压力传感器,型号为华科公司的HK2000G脉搏传感器。利用这种传感器合理设计系统,采集到的脉搏信号能较好地达到要求标准。

选用ADI公司的仪器放大器AD620来放大采集到的脉搏信号。AD620非常适合于压力感测方面的应用。设计系统需要采集三路脉象信号,为了节省脉象信号模拟数字转换和滤波的成本,在信号的前端,设计模拟多路开关,进行多路复用功能。脉象信号较微弱时,为了较少地引入噪声,采用AD7501模拟开关。

A/D转换器选用内带采样保持器、高精度基准电源、内部时钟和三态缓冲的数据输出AD678。它是12位分别率,5μs转换时间的ADC。具有外部结构简单,使用方便,精度高的特点。

评论