1553B总线电缆网络自动测试系统设计及研究

系统功能模块

本系统的某些模块可以直接选用现有模块来实现,其中负责整个系统测试控制流程、数据分析、算法实现等工作的系统控制处理器,采用稳定性很好的工控机来实现;人机交互部分配合工控机选用液晶显示器、键盘鼠标、打印机(实现测试结果报表的打印输出),并结合测试界面软件来实现;数据采集以及阻抗分析模块采用具有编程接口的数字示波器来实现。

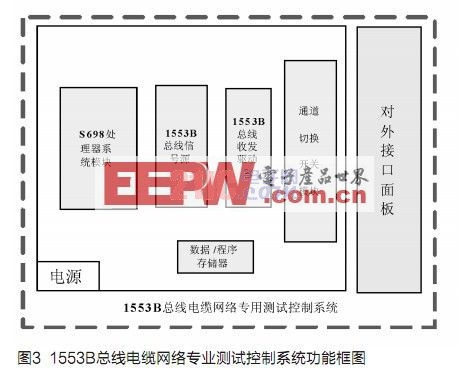

专用测试控制器

1553B总线电缆网络专用测试控制器有两大功能:作为电缆测试的信号源,产生测试用的标准1553B数字信号以及正弦波等激励信号;完成测试过程中信号源输入以及信号采集端的切换。专用测试控制器的功能框图如图3所示。

处理器系统模块以及1553B总线信号源控制器模块采用FPGA Cyclone III EP3C55F484 装载S698 IP核+1553B IP核的形式来实现。珠海欧比特公司自主研发的S698 IP核是一款可裁减的基于AMBA总线架构的内核,片内带有丰富的外设,具有很好的可靠性,已广泛运用于航空航天领域。1553B IP核也是欧比特公司专门为航空、航天测控网络中的设备开发的符合1553B协议的总线控制器模块。该模块内部实现了1553B总线协议处理器和总线数据收发器,可以完成总线控制器(BC)、远程终端(RT)和总线监视器(BM)三种总线设备的功能。此处S698 IP核和1553B IP核均具有可剪裁性,根据测试系统的需要可以对其功能进行增加或减除。1553B软核在FPGA内部实现全部MIL-STD-1553B总线协议的硬件解析,但1553B信号电平的逻辑转换、驱动需要在外部通过收发驱动器实现。这里选用HOLT公司的1553B总线收发驱动器HI-1573进行设计。

综合考虑系统的功能需求,程序存储器采用了SST公司的8位FLASH,型号为39VF040(512×8bit),占用处理器的地址范围为:0x0000000~0x0007ffff;数据存储器采用了ISSI公司的16位SRAM,型号为IS61LV51216(512×16bit),占用处理器的地址范围为:0x4000000~ 0x400fffff。

通道切换开关模块主要完成激励信号选择性输入到被测网络以及选择性采集被测网络上的数据信号,因此用于选择导通的开关必须具有导通电阻小、导通电容小等特性,从而极大减小开关对激励信号或被采集信号的影响。综合考虑各方面因素,选择欧姆龙继电器进行设计。

为了最大限度地兼容通用的1553B总线电缆网络的接入测试,接口面板按照可接入32路1553B总线电缆网络端点的需求来设计,同时每组接插件都是由1个孔型(DK-621-0940-4S)和1个针型(DK-621-0940-4P)插座组成,以兼容外部的针型(DK-621-0939-4P)和孔型插头(DK-621-0939-4S)。

评论